**Document Identifier: DSP2067**

Date: 2023-11-20

Version: 0.6.0

# PLDM CXL Memory Modeling

#### **Information for Work-in-Progress version:**

**IMPORTANT:** This document is not a standard. It does not necessarily reflect the views of DMTF or its members. Because this document is a Work in Progress, this document may still change, perhaps profoundly and without notice. This document is available for public review and comment until superseded.

Provide any comments through the DMTF Feedback Portal: http://www.dmtf.org/ standards/feedback

**Supersedes: None**

**Document Class: Informational**

**Document Status: Work in Progress**

**Document Language: en-US**

Copyright Notice

Copyright © 2023-2023 DMTF. All rights reserved.

DMTF is a not-for-profit association of industry members dedicated to promoting enterprise and systems management and interoperability. Members and non-members may reproduce DMTF specifications and documents, provided that correct attribution is given. As DMTF specifications may be revised from time to time, the particular version and release date should always be noted.

Implementation of certain elements of this standard or proposed standard may be subject to third party patent rights, including provisional patent rights (herein "patent rights"). DMTF makes no representations to users of the standard as to the existence of such rights, and is not responsible to recognize, disclose, or identify any or all such third party patent right, owners or claimants, nor for any incomplete or inaccurate identification or disclosure of such rights, owners or claimants. DMTF shall have no liability to any party, in any manner or circumstance, under any legal theory whatsoever, for failure to recognize, disclose, or identify any such third party patent rights, or for such party's reliance on the standard or incorporation thereof in its product, protocols or testing procedures. DMTF shall have no liability to any party implementing such standard, whether such implementation is foreseeable or not, nor to any patent owner or claimant, and shall have no liability or responsibility for costs or losses incurred if a standard is withdrawn or modified after publication, and shall be indemnified and held harmless by any party implementing the standard from any and all claims of infringement by a patent owner for such implementations.

For information about patents held by third-parties which have notified DMTF that, in their opinion, such patent may relate to or impact implementations of DMTF standards, visit <a href="http://www.dmtf.org/about/policies/disclosures.php">http://www.dmtf.org/about/policies/disclosures.php</a>.

This document's normative language is English. Translation into other languages is permitted.

## CONTENTS

| 1 | Foreword                                            | . 5 |

|---|-----------------------------------------------------|-----|

|   | 1.1 Acknowledgments                                 | . 5 |

| 2 | Introduction                                        |     |

|   | 2.1 Document conventions                            | . 6 |

|   | 2.1.1 Typographical conventions                     | . 6 |

|   | 2.1.2 ABNF usage conventions                        | . 6 |

|   | 2.1.3 Reserved and unassigned values                | . 6 |

|   | 2.1.4 Byte ordering                                 | . 6 |

| 3 | Scope                                               | . 7 |

| 4 | Normative references                                | . 8 |

| 5 | Terms and definitions                               | 10  |

| 6 | Symbols and abbreviated terms                       | 11  |

| 7 | PLDM CXL Memory Device Modeling overview            | 12  |

|   | 7.1 Model Elements                                  | 12  |

|   | 7.1.1 PLDM terminus                                 | 12  |

|   | 7.1.2 CXL Memory Board (CMB)                        | 13  |

|   | 7.1.3 CXL Memory Module (CMM)                       | 13  |

|   | 7.1.4 CXL Memory Controller                         | 13  |

|   | 7.1.5 Power Management Integrated Circuit (PMIC)    | 13  |

|   | 7.1.6 Memory Slot                                   | 14  |

|   | 7.1.7 Memory Module                                 | 14  |

|   | 7.1.8 Memory Media                                  | 14  |

|   | 7.1.9 Memory Unit                                   | 14  |

|   | 7.2 Model Sensors                                   | 14  |

|   | 7.2.1 Sensors Overview                              |     |

|   | 7.2.2 CMD Temperature sensor                        | 16  |

|   | 7.2.3 CMD Power sensor.                             | 16  |

|   | 7.2.4 CMD Composite state sensor.                   |     |

|   | 7.2.5 CMD Aggregated temperature sensor             |     |

|   | 7.2.6 CMD Thermal Throttle Enable Effecter          |     |

|   | 7.2.7 CMD Power Throttle Enable Effecter            |     |

|   | 7.2.8 CXL Memory Controller Temperature sensor      |     |

|   | 7.2.9 CXL Memory Controller Power sensor            | 17  |

|   | 7.2.10 PMIC Temperature sensor                      | 17  |

|   | 7.2.11 PMIC Power sensor                            |     |

|   | 7.2.12 PMIC Current sensor                          |     |

|   | 7.2.13 PMIC Fault sensor                            |     |

|   | 7.2.14 Memory Module Presence sensor                |     |

|   | 7.2.15 DIMM temperature sensor                      |     |

|   | 7.3 Hierarchy description of the CMD model elements |     |

|   | 7.3.1 Physical Entity Association                   | 18  |

|   |                                                     |     |

|     | 7.3.2 Logical Entity Association                             | 20 |

|-----|--------------------------------------------------------------|----|

|     | 7.3.3 Sensor association                                     | 21 |

|     | 7.3.3.1 Associating a sensor at the top level                | 22 |

|     | 7.4 Element PLDM Type IDs                                    | 22 |

|     | 7.5 Enumeration                                              | 23 |

|     | 7.5.1 Enumeration scheme                                     | 23 |

|     | 7.6 Model illustration                                       | 25 |

|     | 7.6.1 CXL Memory Device                                      | 25 |

|     | 7.6.2 CXL Memory Controller Hierarchy                        | 26 |

|     | 7.6.3 Memory Module Hierarchy                                | 26 |

|     | 7.6.4 Memory Media Hierarchy                                 | 26 |

|     | 7.7 Events                                                   | 26 |

|     | 7.7.1 CXL Memory Controller firmware version change          | 26 |

|     | 7.7.2 Health and State sensors events notifications          | 26 |

| 8 ] | Model Use example                                            | 28 |

|     | 8.1 Model hierarchy                                          |    |

|     | 8.2 Top-level TID                                            |    |

|     | 8.3 CXL Memory Device Model                                  |    |

|     | 8.3.1 CXL Memory Device Temperature Sensor PDR               |    |

|     | 8.3.2 CXL Memory Device Power Sensor PDR                     |    |

|     | 8.3.3 CXL Memory Device Composite State Sensor PDR           |    |

|     | 8.3.4 CXL Memory Device Aggregated Temperature Sensor PDR    |    |

|     | 8.3.5 CXL Memory Device Thermal Throttle Enable Effecter PDR |    |

|     | 8.3.6 CXL Memory Device Power Throttle Enable Effecter PDR   |    |

|     | 8.4 CXL Memory Controller Model                              |    |

|     | 8.4.1 CXL Memory Controller Temperature Sensor PDR           |    |

|     | 8.4.2 CXL Memory Controller Power Sensor PDR                 |    |

|     | 8.5 PMIC                                                     |    |

|     | 8.5.1 PMIC Temperature Sensor PDR                            |    |

|     | 8.5.2 PMIC Power Sensor PDR                                  |    |

|     | 8.5.3 PMIC Current Sensor PDR                                |    |

|     | 8.5.4 PMIC Fault Sensor PDR                                  |    |

|     | 8.6 DIMM Slot                                                |    |

|     | 8.6.1 DIMM Presence Sensor PDR                               |    |

|     | 8.7 DIMM                                                     |    |

|     | 8.7.1 DIMM Temperature Sensor PDR                            | 46 |

# 1 Foreword

The *PLDM CXL Memory Modeling (DSP2067)* was prepared by the Platform Management Communications Infrastructure (PMCI) Working Group of the DMTF.

DMTF is a not-for-profit association of industry members dedicated to promoting enterprise and systems management and interoperability. For information about the DMTF, see <a href="http://www.dmtf.org">http://www.dmtf.org</a>.

# 1.1 Acknowledgments

The DMTF acknowledges the following individuals for their contributions to this document:

#### **DMTF Contributors:**

- Patrick Caporale Lenovo

- Yuval Itkin NVIDIA Corporation

- Eliel Louzoun Intel Corporation

- Hemal Shah Broadcom Inc.

#### **CXL Consortium Contributors:**

- Deepaganesh Paulraj Dell Technologies

- Jordan Chin Dell Technologies

- · Rama Rao Bisa Dell Technologies

- Vaishnavi S Dell Technologies

# 2 Introduction

This document describes a modeling scheme for CXL Memory using PLDM for Monitoring and Control DSP0248 semantics.

#### 2.1 Document conventions

#### 2.1.1 Typographical conventions

The following typographical conventions are used in this document:

- Document titles are marked in italics.

- · ABNF rules are in monospaced font.

#### 2.1.2 ABNF usage conventions

Format definitions in this document are specified using ABNF (see RFC5234), with the following deviations:

Literal strings are to be interpreted as case-sensitive Unicode characters, as opposed to the definition in RFC5234 that interprets literal strings as case-insensitive US-ASCII characters.

#### 2.1.3 Reserved and unassigned values

Unless otherwise specified, any reserved, unspecified, or unassigned values in enumerations or other numeric ranges are reserved for future definition by the DMTF.

Unless otherwise specified, numeric or bit fields that are designated as reserved shall be written as 0 (zero) and ignored when read.

#### 2.1.4 Byte ordering

Unless otherwise specified, byte ordering of multi-byte numeric fields or bit fields is "Big Endian" (that is, the lower byte offset holds the most significant byte, and higher offsets hold lesser significant bytes).

# 3 Scope

This document defines example data models for implementing the above-described generic device management of CXL memory devices using PLDM for Platform Monitoring and Control DSP0248 semantics. This document establishes a common framework that can provide implementation consistency between a system's Management Controller and CXL memory devices connected to the system. While this document focuses on CXL cards with DIMM expansion slots and CXL modules with embedded memory, these data models are assumed to be extensible to a variety of physical implementations and should not be construed to be limited to the examples herein.

# **4 Normative references**

The following referenced documents are indispensable for the application of this document. For dated or versioned references, only the edition cited (including any corrigenda or DMTF update versions) applies. For references without a date or version, the latest published edition of the referenced document (including any corrigenda or DMTF update versions) applies.

Unless otherwise specified, for DMTF documents this means any document version that has minor or update version numbers that are later than those for the referenced document. The major version numbers must match the major version number given for the referenced document.

DMTF DSP0236, *MCTP Base Specification, 1.3* https://www.dmtf.org/sites/default/files/standards/documents/DSP0236\_1.3.X.pdf

DMTF DSP0240, *Platform Level Data Model (PLDM) Base Specification, 1.1* https://www.dmtf.org/sites/default/files/standards/documents/DSP0240 1.1.X.pdf

DMTF DSP0241, *Platform Level Data Model (PLDM) Over MCTP Binding Specification, 1.0* https://www.dmtf.org/sites/default/files/standards/documents/DSP0241 1.0.X.pdf

DMTF DSP0245, *Platform Level Data Model (PLDM) IDs and Codes Specification, 1.3* https://www.dmtf.org/sites/default/files/standards/documents/DSP0245\_1.3.X.pdf

DMTF DSP0248, Platform Level Data Model (PLDM) for Platform Monitoring and Control Specification, 1.2 https://www.dmtf.org/sites/default/files/standards/documents/DSP0248\_1.2.X.pdf

DMTF DSP0249, Platform Level Data Model (PLDM) State Sets Specification, 1.1 https://www.dmtf.org/sites/default/files/standards/documents/DSP0249\_1.1.X.pdf

DMTF DSP0257, Platform Level Data Model (PLDM) FRU Data Specification, 1.0 https://www.dmtf.org/sites/default/files/standards/documents/DSP0257\_1.0.X.pdf

DMTF DSP0267, *Platform Level Data Model (PLDM) for Firmware Update Specification, 1.1* https://www.dmtf.org/sites/default/files/standards/documents/DSP0267\_1.2.X.pdf

DMTF DSP2054, Platform Level Data Model (PLDM) NIC Modeling Specification, 1.0 http://dmtf.org/sites/default/files/standards/documents/DSP2054\_1.0.X.pdf

DMTF DSP2061, *PLDM Accelerator Modeling Specification*, 1.0 http://dmtf.org/sites/default/files/standards/documents/DSP2061\_1.0.X.pdf

IETF RFC2781, UTF-16, an encoding of ISO 10646, February 2000 http://www.ietf.org/rfc/rfc2781.txt

IETF STD63, UTF-8, a transformation format of ISO 10646 http://www.ietf.org/rfc/std/std63.txt

IETF RFC4122, A Universally Unique Identifier (UUID) URN Namespace, July 2005 http://www.ietf.org/rfc/rfc4122.txt

IETF RFC4646, Tags for Identifying Languages, September 2006 http://www.ietf.org/rfc/rfc4646.txt

ISO 8859-1, Final Text of DIS 8859-1, 8-bit single-byte coded graphic character sets — Part 1: Latin alphabet No.1, February 1998

ISO/IEC Directives, Part 2, Rules for the structure and drafting of International Standards https://www.iso.org/sites/directives/current/part2/index.xhtml

IETF RFC5234, ABNF: Augmented BNF for Syntax Specifications, January 2008 http://tools.ietf.org/html/rfc5234

# 5 Terms and definitions

In this document, some terms have a specific meaning beyond the normal English meaning. Those terms are defined in this clause.

The terms "shall" ("required"), "shall not", "should" ("recommended"), "should not" ("not recommended"), "may", "need not" ("not required"), "can" and "cannot" in this document are to be interpreted as described in ISO/IEC Directives, Part 2, Clause 7. The terms in parentheses are alternatives for the preceding term, for use in exceptional cases when the preceding term cannot be used for linguistic reasons. Note that ISO/IEC Directives, Part 2, Clause 7 specifies additional alternatives. Occurrences of such additional alternatives shall be interpreted in their normal English meaning.

The terms "clause", "subclause", "paragraph", and "annex" in this document are to be interpreted as described in ISO/IEC Directives, Part 2, Clause 6.

The terms "normative" and "informative" in this document are to be interpreted as described in ISO/ IEC Directives, Part 2, Clause 3. In this document, clauses, subclauses, or annexes labeled "(informative)" do not contain normative content. Notes and examples are always informative elements.

Refer to DSP0240 for terms and definitions that are used across the PLDM specifications.

# 6 Symbols and abbreviated terms

Refer to DSP0240 and DSP0248 for symbols and abbreviated terms that are used across the PLDM specifications. For the purposes of this document, the following additional symbols and abbreviated terms apply.

#### **PCB**

Printed Circuit Board

#### **CMB**

CXL Memory Board

#### **CMD**

**CXL Memory Device**

#### **CMM**

CXL Memory Module

#### **DIMM**

Dual In-line Memory Module

#### **PMIC**

Power Management Integrated Circuit

# 7 PLDM CXL Memory Device Modeling overview

This document describes two hierarchical modeling schemes for CXL Memory Devices using PLDM for Platform Monitoring and Control DSP0248 semantics:

- CXL Memory Board (CXL Memory Device with DIMM Expansion)

- CXL Memory Module (CXL Memory Device with Embedded Memory)

The term CXL Memory Device is used to refer to both the models. The models are scalable and allow consistent modeling of CXL Memory Devices with different configuration options.

While PLDM for Platform Monitoring and Control DSP0248 is a published standard, using the models defined in this document simplifies interoperability by establishing a consistent schema.

The basic format that is used for sending PLDM messages is defined in DSP0240. The format that is used for carrying PLDM messages over a transport-layer protocol and medium is given in companion documents to the base specification. For example, DSP0241 defines how PLDM messages are formatted and sent using MCTP as the transport.

The model supports the following:

- Consistent modeling of a CXL memory device regardless of the specific configuration and resource count

- CXL memory device hardware structure description

- Reporting of configuration changes such as firmware update

#### 7.1 Model Elements

#### 7.1.1 PLDM terminus

PLDM for Platform Monitoring and Control DSP0248 defines a single root for every device instance, referred to as PLDM Terminus and identified with a TID. The term **MC** is used to identify a PLDM terminus which communicates with a CXL Memory Controller on the device throughout this document.

When there are multiple CXL Memory Controllers assembled on the same device, there may be a single CXL Memory Controller which reports all the sensors of all the elements on the CXL Memory

Device to the MC. Alternatively, each CXL Memory Controller in the CXL Memory Device may present a separate PLDM terminus.

PLDM for Platform Monitoring and Control DSP0248 does not allow associating components reported via different PLDM termini since every database is relative to a given PLDM terminus. To overcome this constraint, the implementers can retrieve a globally unique ID (Board part number and serial number) from each TID and recognize these TIDs belonging to the same CXL Memory Device. The process to retrieve the globally unique ID (Board part number and serial number) from each TID is outside of this document.

All PLDM IDs specified by the models in this document shall be consistent across all TIDs on a given card. This avoids conflict from duplication of IDs in the combined model, generated by merging the TID-specific model elements reported as part of the overall model.

#### 7.1.2 CXL Memory Board (CMB)

In this model, the CXL Memory Board is top-level element of the hierarchy containing one or more CXL Memory Controllers on a PCB. The CMB is a hardware solution that provides volatile and/or non-volatile Host-managed Device Memory (HDM) using CXL semantics and has one or more Memory Slots where DIMMs can be inserted. The CMB in this document refers to various form factors and is represented with PLDM Entity ID code 65 for **Memory Board**. CMB may contain sensors such as temperature, power-consumption, and health state.

#### 7.1.3 CXL Memory Module (CMM)

In this model, the CXL Memory Module (CMM) is top-level element of the hierarchy containing one or more CXL Memory Controllers on a PCB. The CMM is a hardware solution that provides volatile and/or non-volatile Host-managed Device Memory (HDM) using CXL semantics. The CMM in this document refers to various form factors and is represented with PLDM Entity ID code 66 for **Memory Module**. The CMM may contain sensors such as temperature, power-consumption, and health state.

#### 7.1.4 CXL Memory Controller

In both above hierarchy models, the CXL memory controller is the second level element of the hierarchy containing one or more sensors. A CXL memory controller is a hardware device with a main function of providing host-access to its attached memory using CXL semantics. A CXL memory controller is represented with PLDM Entity ID code 143 for **Memory controller** and may contain sensors such as power-consumption, and temperature.

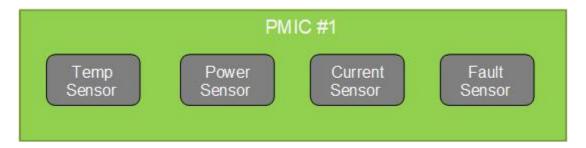

#### 7.1.5 Power Management Integrated Circuit (PMIC)

The term PMIC in this document refers to the power management ICs (or voltage regulators) on a CXL Memory Device or on DIMM that regulate power for the CXL memory controller and/or memory units.

In this model, PMICs regulate the power for the CXL memory controller and other ancillary components is at the second level of the hierarchy. PMICs exclusively regulating power for a memory Slot or Memory Module is considered at the third level of the hierarchy. PMICs are represented with PLDM Entity ID code 124 for **DC-DC converter** and may contain sensors such as fault state, power-consumption, current-consumption, and temperature.

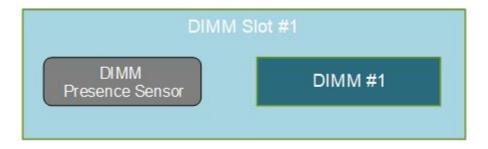

#### 7.1.6 Memory Slot

The term Memory Slot in this document represents the DIMM sockets mounted on the CXL Memory Board that allows to insert Memory Module such as DIMM. In the CMB model, the Memory Slot is considered at the second level of the hierarchy. Memory Slot is represented with PLDM Entity ID code 186 for **Slot** and may contain sensors such as Presence Sensor.

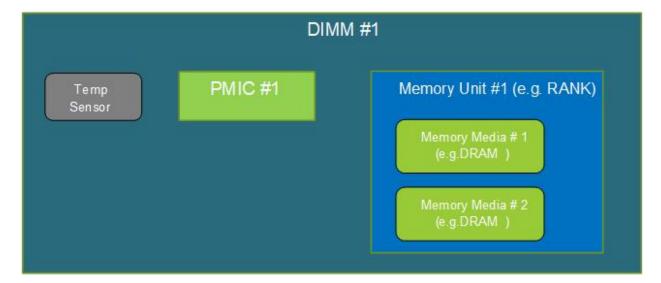

#### 7.1.7 Memory Module

The term Memory Module in this document covers the DIMMs connected via Memory Slots present in the CMB. In this model, the Memory Module is at the third level of the hierarchy. Memory Module is represented with PLDM Entity ID code 66 for **Memory Module** and may contain other entities such as PMICs and sensors such as temperature.

#### 7.1.8 Memory Media

The term Memory Media in this document covers the internal memory chips such as DRAM components, SRAM components, NAND components present on the CMM or Memory Module (DIMM). In this model, the Memory Media soldered directly onto the CMM is considered at the second level of the hierarchy. The Memory Media soldered onto the Memory Module (DIMM) which is inserted in the Memory slots of the CMB is considered at the fourth level of the hierarchy. Memory Media is represented with PLDM Entity ID code 142 for **Memory Chip**.

#### 7.1.9 Memory Unit

The term Memory Unit in this document represents the logical entity such as Rank for DDR, Bank for HBM which is a Logical grouping of 1 to 40 Memory Medias (e.g., DRAM Die). Memory Unit is represented with PLDM Entity ID code **TBD**.

#### 7.2 Model Sensors

#### 7.2.1 Sensors Overview

Attributes are reported by means of sensors. Numeric sensors are used to report specific measured attributes. State sensors report operational and/or health state. The default thresholds for all numeric sensors shall be set by the hardware vendor. The sensors can be associated with any entity such as

the CXL Memory Device, CXL Memory Controller. The description of each sensor is applicable only for the implemented sensors and it is not mandatory to implement all the sensors described in this document. There may be auxiliary devices present on the CMD and each auxiliary device may present its own set of sensors.

Note: The Sensor Auxiliary Names PDR is recommended to provide the proper name of each sensor.

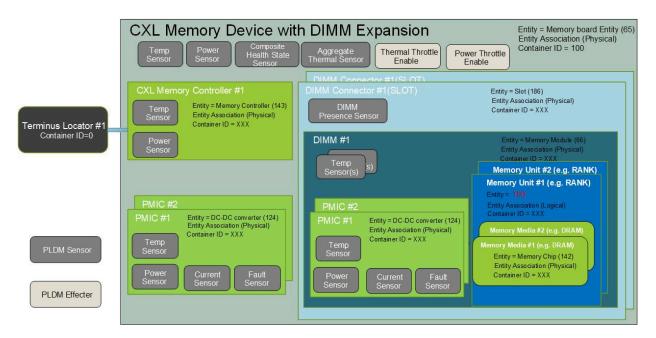

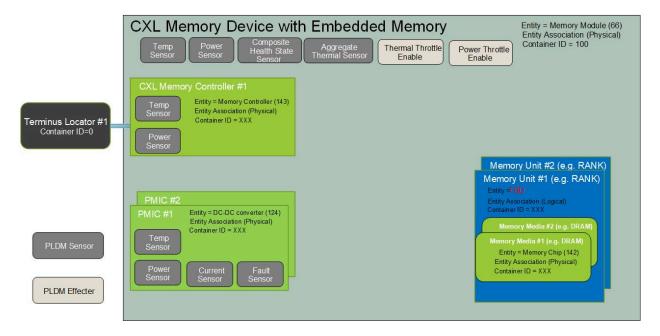

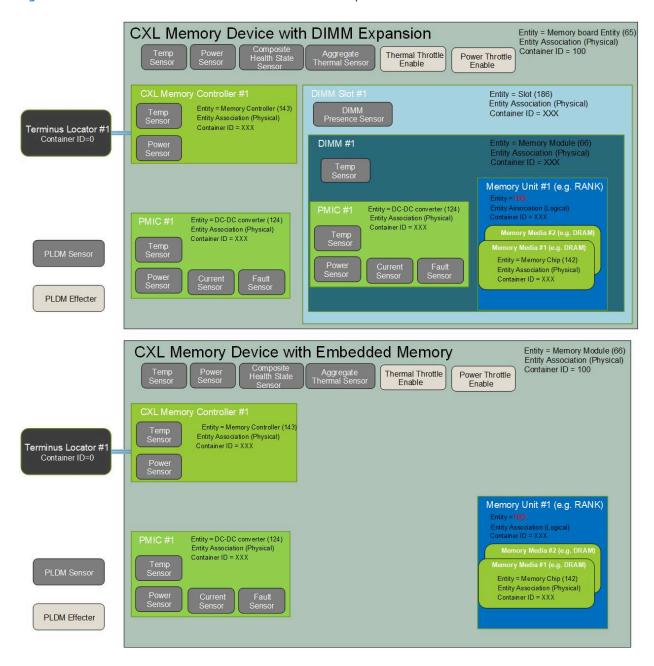

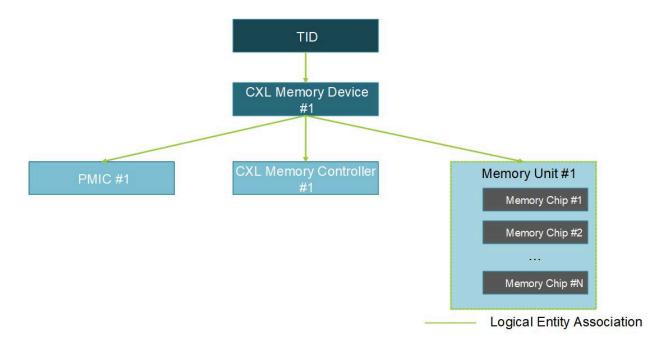

Figure 1 — CXL Memory Board — PLDM model diagram

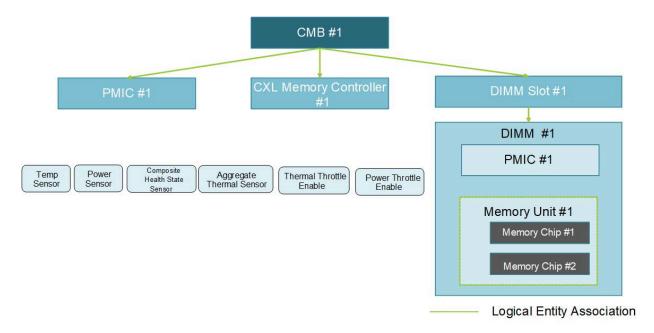

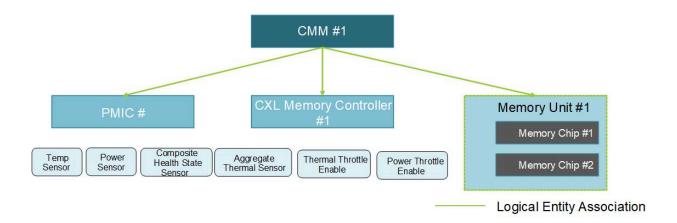

#### Figure 2 — CXL Memory Module — PLDM model diagram

#### 7.2.2 CMD Temperature sensor

The temperature sensor on the CMD (both CMB and CMM) reports the card ambient temperature and is represented using a numeric sensor. There may be multiple temperature sensors installed on the CMD. The sensor unit is 2 (Degree C). Refer to the SensorUnits enumeration table of DSP0248.

#### 7.2.3 CMD Power sensor

The power sensor on the CMD (both CMB and CMM) reports the estimated or measured aggregate power consumption of the CMD and is represented using a numeric sensor. The CMD which cannot accurately report its real-time power consumption may report its estimated maximal power. The sensor unit is 7 (Watts). Refer to the SensorUnits enumeration table of DSP0248.

#### 7.2.4 CMD Composite state sensor

The CMD composite state sensor combines following sensors.

- 1. CMD Thermal state sensor (Thermal Trip).

- 2. CMD health status sensor.

- 3. CMD PMIC fault sensor status.

#### 7.2.5 CMD Aggregated temperature sensor

The temperature sensor on the CMD reports the consolidated temperature of all the subcomponents present in the devices and it is represented using a numeric sensor. The sensor unit is 2 (Degree C). Refer to the SensorUnits enumeration table of DSP0248. There may be multiple memory temperature sensors installed on the internal memory, on the soldered memory, and on the DIMMs.

Note:- If temperature readings via the CXL Component Command Interface is implemented by the CMD, then the value of this temperature sensor should report out the same reading.

#### 7.2.6 CMD Thermal Throttle Enable Effecter

The Thermal Throttle Enable Effecter on the CMD attempts to keep the running average temperature reading from all PLDM temperature sensors below their programmed thresholds by self-throttling device performance. The Set ID is 14 (Performance). Refer to Table 1 (General State Sets) of DSP0249.

#### 7.2.7 CMD Power Throttle Enable Effecter

The Power Throttle Enable Effecter on the CMD attempts to keep the running average power reading

from all PLDM power sensors below their programmed thresholds by self-throttling device performance. The Set ID is 14 (Performance). Refer to Table 1 (General State Sets) of DSP0249.

- 1 Normal = Power throttling is not enabled

- 2 Throttled = Power throttling is enabled to keep all running average power sensor readings below their warning thresholds

- 3 Degraded = Power throttling is enabled to keep all running average power sensor readings below their critical thresholds

#### 7.2.8 CXL Memory Controller Temperature sensor

The temperature sensor on the CXL Memory Controller reports the internal ASIC temperature and is represented using a numeric sensor. The sensor unit is 2 (Degree C). Refer to the SensorUnits enumeration table of DSP0248. The thresholds used by the sensor to define its normal, warning, critical, and fatal ranges are design specific and should be defined by the device manufacturer.

#### **7.2.9 CXL Memory Controller Power sensor**

The power sensor on the CXL Memory Controller reports the estimated or measured aggregate power consumption of the CXL Memory Controller and is represented using a numeric sensor. The CXL Memory Controller which cannot accurately report its real-time power consumption may report its estimated maximal power. The sensor unit is 7 (Watts). Refer to the SensorUnits enumeration table of DSP0248. The thresholds which may be used by the sensor to define its normal, warning, critical, and fatal ranges are design specific and should be defined by the device manufacturer.

#### 7.2.10 PMIC Temperature sensor

The temperature sensor on the PMIC reports the Power Management IC temperature and is represented using a numeric sensor. The sensor unit is 2 (Degree C). Refer to the SensorUnits enumeration table of DSP0248. The thresholds used by the sensor to define its normal, warning, critical, and fatal ranges are design specific and should be defined by the device manufacturer.

#### 7.2.11 PMIC Power sensor

The power sensor on the PMIC reports the estimated or measured aggregate power consumption of the sub-components powered via the respective Power Management IC and is represented using a numeric sensor. The PMIC which cannot accurately report its real-time power consumption may report its estimated maximal power. The sensor unit is 7 (Watts). Refer to the SensorUnits enumeration table of DSP0248. The thresholds which may be used by the sensor to define its normal, warning, critical, and fatal ranges are design specific and should be defined by the device manufacturer.

#### 7.2.12 PMIC Current sensor

The current sensor on the PMIC reports the estimated or measured current consumption of the sub-components powered via the respective Power Management IC and is represented using a numeric sensor. The PMIC which cannot accurately report its real-time power consumption may report its estimated maximal power. The sensor unit is 6 (Amps). Refer to the SensorUnits enumeration table of DSP0248. The thresholds which may be used by the sensor to define its normal, warning, critical, and fatal ranges are design specific and should be defined by the device manufacturer.

#### 7.2.13 PMIC Fault sensor

The Fault sensor on the PMIC reports its current power supply state since last known power cycle. The Set ID is 256 (Power Supply State). Refer to Table 9 (Power-Related State Sets) of DSP0249.

If PMIC implementations are based on JEDEC standard power management ICs, then the PLDM sensor state readings should follow the following mapping guidance:

#### 7.2.14 Memory Module Presence sensor

The Memory Module Presence sensor of the Memory Slot indicates whether a DIMM is present in the Slot / Connector or not and is represented using a State sensor. The Set ID is 13 (Presence). Refer to Table 1 (General State Sets) of DSP0249.

#### 7.2.15 DIMM temperature sensor

The temperature sensor on the DIMM reports the DIMM ambient temperature and is represented using a numeric sensor. The sensor unit is 2 (Degree C). Refer to the SensorUnits enumeration table of DSP0248. Sensor calibration and the thresholds used by the sensor to define its normal, warning, critical, and fatal ranges are design specific and should be defined by the device manufacturer.

# 7.3 Hierarchy description of the CMD model elements

PLDM CMD Modeling uses a hierarchical model. Refer to section 10 PLDM associations and section 11 Entity Association PDR of DSP0248 to understand physical and logical associations.

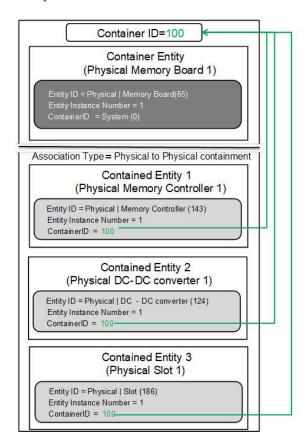

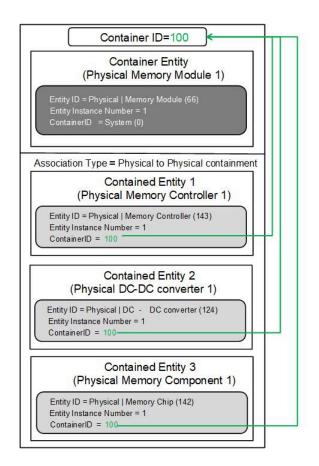

#### 7.3.1 Physical Entity Association

Physical association is defined in DSP0248 as a method to associate components which are physically connected to each other. The model uses this concept to describe the following structures:

· Content of the CXL Memory Device

- · Content of the CXL Memory Controller

- Content of the PMIC

- · Content of the Memory Slot

- · Content of the Memory Module

- · Content of the Memory Media

A hierarchy entity is defined using an entity association PDR identified with a unique **ContainerID** identifier parameter. The entity association PDR **ContainerEntityContainerID** references the PDR in which the entity is contained.

Figure 3 and 4 show the examples of how an CMD entity association PDR references its container entity and contained entities:

| CXL Memory             | Board         | - Entity Association PDR       |  |  |

|------------------------|---------------|--------------------------------|--|--|

| Container ID           | to the second | 100                            |  |  |

| Container E            | ntity -       | - CXL Memory Board 1           |  |  |

| Entity Type            | 65            | Memory Board                   |  |  |

| Entity Instance Number | 1             |                                |  |  |

| ContainerID            | 0             | System                         |  |  |

|                        | ),<br>        | #KC # 100 miles                |  |  |

| Association Type       | Phys          | sical to Physical containment  |  |  |

|                        |               |                                |  |  |

| Contained En           | tity 1 -      | <b>CXL Memory Controller 1</b> |  |  |

| Entity Type            | 143           | CXL Memory Controller          |  |  |

| Entity Instance Number | 1             | *                              |  |  |

| Containerl D           | 100           | CXL Memory Board 1             |  |  |

|                        | 0.            | We have a second to the second |  |  |

| Contair                | ned En        | tity 2 - PMIC 1                |  |  |

| Entity Type            | 124           |                                |  |  |

| Entity Instance Number | 1             | N. 9 . 111                     |  |  |

| ContainerID            | 100           | CXL Memory Board 1             |  |  |

|                        |               | - to                           |  |  |

| Contained E            | ntity 3       | - DIMM Connector 1             |  |  |

| Entity Type            | 186           | Slot                           |  |  |

| Entity Instance Number | 1             | 2 931                          |  |  |

| Container D            | 100           | CXL Memory Board 1             |  |  |

Figure 3 — Hierarchy description using ContainerEntityContainerID referencing the ContainedEntityContainerID

| Container ID              |         | 100                               |

|---------------------------|---------|-----------------------------------|

| Container E               | ntity – | CXL Memory Module 1               |

| Entity Type               | 66      | Memory Module                     |

| Entity Instance Number    | 1       |                                   |

| ContainerID               | 0       | System                            |

| Association Type          | Physic  | al to Physical containment        |

| Contained Ent             | ity 1 - | CXL Memory Controller             |

| Entity Type               | 143     | CXL Memory Controller             |

| Entity Instance Number    | 1       |                                   |

| ContainerID               | 100     | CXL Memory Module 1               |

| Contain                   | ned Er  | ntity 2 - PMIC 1                  |

| Entity Type               | 124     | DC - DC converter                 |

| Entity Instance Number    | 1       |                                   |

|                           | 100     | CXL Memory Module 1               |

| Container D               |         |                                   |

| ContainerID  Contained En | tity 3  | - Memory Component 1              |

|                           | 142     | - Memory Component 1  Memory Chip |

| Contained En              | 142     | T                                 |

Figure 4 — Hierarchy description using ContainerEntityContainerID referencing the ContainedEntityContainerID

#### 7.3.2 Logical Entity Association

The DSP0248 defines logical association as a method to associate components which collectively form a shared property yet are not physically part of the same component. This type of association is typically used to group items that have a common parameter that is monitored or controlled. This model uses logical association to describe the following structures:

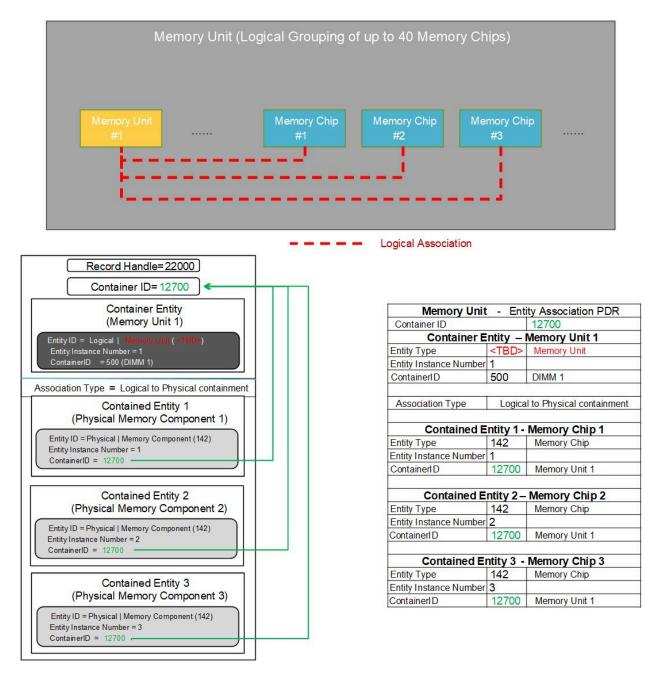

Figure 5 shows logical association between the Memory Unit and a Memory Media:

Figure 5 — Logical Containment PDR

#### 7.3.3 Sensor association

As per DSP0248, numeric and state sensors are not included inside entity association PDRs. They are instead associated to the measured entity by directly referencing the EntityContainerID, EntityType,

and EntityInstanceNumber of the measured entity in an entity association PDR. A sensor is identified by a unique Sensor ID value.

#### 7.3.3.1 Associating a sensor at the top level

When associating a sensor to the top-level entity which is the system the association uses the top-level *ContainerEntityType, ContainerEntityInstanceNumber* and *ContainerEntityContainerID* parameters.

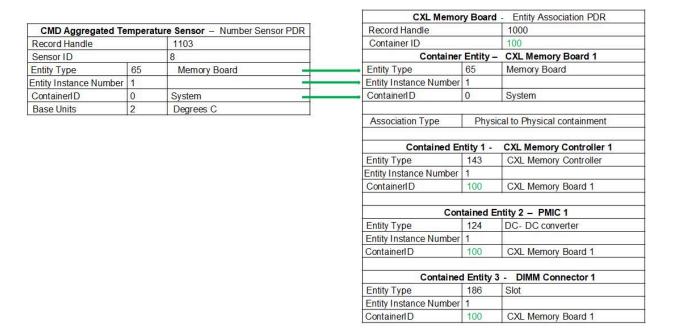

Figure 6 illustrates the association of an Aggregated temperature sensor to the CXL Memory Device in the model.

Figure 6 — Top-level sensor association

# 7.4 Element PLDM Type IDs

The model uses the following Type ID for each component in the model, selected from the available types defined in DSP0249. The following table lists the chosen Type IDs used in the model:

Table 1 — Entity IDs used in CXL Memory Model

| Component | PLDM Entity  | Entity ID |

|-----------|--------------|-----------|

| СМВ       | Memory Board | 65        |

| Component                       | PLDM Entity       | Entity ID   |

|---------------------------------|-------------------|-------------|

| СММ                             | Memory Module     | 66          |

| CXL Memory Controller           | Memory Controller | 143         |

| PMIC                            | DC-DC converter   | 124         |

| Memory Slot (e.g., DIMM Socket) | Slot              | 186         |

| Memory Module (e.g., DIMM)      | Memory Module     | 66          |

| Memory Media (e.g., DRAM Die)   | Memory Chip       | 142         |

| Memory Unit (e.g., Rank)        | <tbd></tbd>       | <tbd></tbd> |

#### 7.5 Enumeration

PLDM for Platform Monitoring and Control DSP0248 uses enumerated IDs to define elements in the database. These IDs are labeled as:

- Container ID unique for each container PDR in the model database

- Instance ID unique for each entity type within a given hierarchy level

- Handle ID unique ID for each PDR in the model database

- Sensor ID unique for each sensor in the model database

The proposed model provides an example enumeration scheme for these IDs, allowing a reasonably scalable formulation. This model is only an example and implementations should not rely on these values.

#### 7.5.1 Enumeration scheme

The model assumes some maximal limits to define the enumerated values. These limits are provided as an example and can be adjusted according to the specific CXL Memory Device requirements.

The example model enumeration is designed to support an CXL Memory Device that does not exceed the following limits:

**Table 2 — Enumeration Limits in CXL Memory Model**

| Component                     | Max Number of Instances |

|-------------------------------|-------------------------|

| CXL Memory Controller per CMD | 4                       |

| PMIC per CMD / per DIMM       | 64                      |

| Memory Slot per CMB           | 16                      |

| Memory Media per DIMM / CMM   | 640                     |

| Memory Unit per DIMM / CMM    | 16                      |

| Temperature sensors per DIMM  | 10                      |

| Others                        | 1                       |

**Note:** If one of the above limits is insufficient for an CXL Memory Device, only the enumerated values will be affected, and the model structure will not have to change.

Figure 7 illustrates the enumeration scheme, calculated based on the above limits.

| item                                                            | Max   | Base<br>Container | Max<br>Container | Base<br>Handl | Max<br>Handl | Base<br>Sensor | Max<br>Sensor | Base<br>Instanc | Max<br>Instanc | Туре        |

|-----------------------------------------------------------------|-------|-------------------|------------------|---------------|--------------|----------------|---------------|-----------------|----------------|-------------|

|                                                                 | count | 10                | 10               |               |              | 10             | 10            |                 |                | ID          |

| CMB                                                             | 1     | 100               |                  | 1000          | 1000         |                |               | 1               | 1              | 65          |

| CMM                                                             | 1     | 100               |                  | 1000          | 1000         |                |               | 1               | 1              | 66          |

| CMD Temp Sensor                                                 | 1     |                   |                  | 1100          | 1100         | 1              | 1             | 1               | 1              | 65 / 66     |

| CMD Power Sensor                                                | 1     |                   |                  | 1101          | 1101         | 2              | 2             | 1               | 1              | 65 / 66     |

| CMD Composite State Sensor<br>CMD Aggregated Temperature Sensor | 1     |                   |                  | 1102          | 1102         | 3              | 3             | 1               | -              | 65 / 66     |

| CMD Thermal Throttle Enable Effecter                            | 1     | _                 |                  | 1103          | 1103         | 5              | 5             | 1               | 1              | 65 / 66     |

| CMD Power Throttle Enable Effecter                              | 1     |                   |                  | 1105          | 1105         | 6              | 6             | 1               | 1              | 65 / 66     |

| CXL Controller                                                  | 4     | 200               | 203              | 2000          | 2003         |                |               | 1               | 4              | 143         |

| CXL Controller Temperature Sensor                               | 4     |                   |                  | 2100          | 2103         | 10             | 13            | 1               | 4              | 143         |

| CXL Controller Power Sensor                                     | 4     |                   |                  | 2200          | 2203         | 20             | 23            | 1               | 4              | 143         |

| PMIC                                                            | 64    | 300               | 363              | 3000          | 3063         |                |               | 1               | 64             | 124         |

| PMIC Temperature Sensor                                         | 64    |                   |                  | 3100          | 3163         | 100            | 163           | 1               | 1              | 124         |

| PMIC Power Sensor                                               | 64    |                   |                  | 3200          | 3263         | 200            | 263           | 1               | 1              | 124         |

| PMIC Current Sensor                                             | 64    |                   |                  | 3300          | 3363         | 300            | 363           | 1               | 1              | 124         |

| PMIC Fault Sensor                                               | 64    |                   |                  | 3400          | 3463         | 400            | 463           | 1               | 1              | 124         |

| Memory Slot                                                     | 16    | 400               | 415              | 4000          | 4015         |                |               | 1               | 16             | 186         |

| Memory Module Presence Sensor                                   | 16    |                   |                  | 4100          | 4115         | 500            | 515           | 1               | 1              | 186         |

| Memory Module                                                   | 16    | 500               | 515              | 5000          | 5015         |                |               | 1               | 1              | 144         |

| Memory Module Temperature Sensor                                | 160   |                   |                  | 5100          | 5259         | 600            | 759           | 1               | 10             | 144         |

| Memory Module - PMIC                                            | 1024  | 600               | 1623             | 6000          | 7023         |                |               | 1               | 64             | 124         |

| Memory Module - PMIC Temperature Sensor                         | 1024  |                   |                  | 7100          | 8123         | 700            | 1723          | 1               | 1              | 124         |

| Memory Module - PMIC Power Sensor                               | 1024  |                   |                  | 8200          | 9223         | 1000           | 2023          | 1               | 1              | 124         |

| Memory Module - PMIC Current Sensor                             | 1024  |                   |                  | 9300          | 10323        | 1300           | 2323          | 1               | 1              | 124         |

| Memory Module - PMIC Fault Sensor                               | 1024  |                   |                  | 10400         | 11423        | 1600           | 2623          | 1               | 1              | 124         |

| CMM- Memory Chip                                                | 640   | 1700              | 2339             | 11500         | 12139        | 100            | 739           | 1               | 640            | 142         |

| Memory Module - Memory Chip                                     | 10240 | 2400              | 12639            | 11500         | 21739        |                |               | - 1             | 640            | 142         |

| CMM Memory Unit                                                 | 16    | 12700             | 12715            | 22000         | 22015        |                |               | 1               | 16             | <tb0></tb0> |

| Memory Module Memory Unit                                       | 256   | 12800             | 13055            | 22000         | 22255        |                |               | 1               | 16             | <tb0></tb0> |

| Calculated                                                      |       |                   |                  |               |              |                |               |                 |                |             |

| Model Constant                                                  |       |                   |                  |               |              |                |               |                 |                |             |

Figure 7 — Example Enumeration Scheme with Type IDs

## 7.6 Model illustration

The CMD PLDM model is a hierarchical model. The following subclauses describe the model for each of the hierarchy levels:

## 7.6.1 CXL Memory Device

The CXL Memory Device top level may have the PCB card, CXL Memory Controllers, Memory Slots, Memory Modules, Memory chips, one or more Temperature sensors, composite state sensor and power

sensor. The PCB power consumption is represented with a power sensor. The CXL Memory Device operational state is represented by a composite state sensor. When there are multiple CXL Memory controllers on the same card, CMD sensors are typically only reported by the first CXL Memory controller. The CXL Memory Device is responsible for determining the order of CXL Memory controllers in the card. Note that the top- level health state sensor of the composite state sensor may reflect the card level sensors and the health states of PMIC, DIMM.

#### 7.6.2 CXL Memory Controller Hierarchy

The CXL Memory Controller hierarchy represents the active device (or one of multiple devices) that performs the CXL Memory Device control interface. The CXL Memory Controller is represented as a collection of sensors associated with it.

#### 7.6.3 Memory Module Hierarchy

The Memory Module hierarchy represents the DIMMs connected via Memory Sockets present in the CMB. The Memory module is represented as a collection of sensors associated with it.

#### 7.6.4 Memory Media Hierarchy

The Memory Media hierarchy represents a memory chip component (or one of multiple components) that that provides volatile and/or non-volatile host-managed device memory (HDM).

#### 7.7 Events

This model supports using PLDM events as a method to notify the MC upon changes in the sensor readings/states as described in DSP0248. The following example events can be used with the model and the implementation may choose to have more events.

#### 7.7.1 CXL Memory Controller firmware version change

This event indicates to the MC that the firmware version of the CXL Memory Device has changed. The MC may use the *GetPDRRepositoryInfo* command and check if the *timestamp* parameter value has changed since it last read the PDRs. The MC may update the whole PDR repository by re-reading all the PDRs. The value used for the *timestamp* can be a virtual time value initialized by the CXL Memory Device at device initialization.

#### 7.7.2 Health and State sensors events notifications

The sensors on the CXL Memory Device may report a change in value, health, or state using a PLDM state or numeric sensor event. Providing such a notification can significantly shorten the response

time, compared to waiting for the MC to poll the sensors, for an occurrence that requires the MC to take an action such as increasing the airflow from a cooling fan.

# 8 Model Use example

The following examples for modeling an CXL Memory Device using PLDM for Platform Monitoring and Control DSP0248 describes an CXL Memory Device with the following attributes:

#### Example 1: -

- Single CXL Memory Board

- Temperature Sensor

- Power Sensor

- Composite State Sensor

- Aggregated Temperature Sensor

- Thermal Throttle Enable Effecter

- Power Throttle Enable Effecter

- Single CXL Memory Controller

- Temperature Sensor

- Power Sensor

- Single PMIC

- Temperature Sensor

- Power Sensor

- Current Sensor

- Fault Sensor

- Single DIMM Slot

- Memory Module Presence sensor

- Single DIMM

- Temperature Sensor

- Single PMIC

- Temperature Sensor

- Power Sensor

- Current Sensor

- Fault Sensor

- Dual Memory Chips on DIMM (logically grouped as single Memory Unit)

#### Example 2: -

- · Single CXL Memory Module

- Temperature Sensor

- Power Sensor

- Composite State Sensor

- Aggregated Temperature Sensor

- Thermal Throttle Enable Effecter

- Power Throttle Enable Effecter

- Single CXL Memory Controller

- Temperature Sensor

- Power Sensor

- Single PMIC

- Temperature Sensor

- Power Sensor

- Current Sensor

- Fault Sensor

- Dual Memory Chips (logically grouped as single Memory Unit)

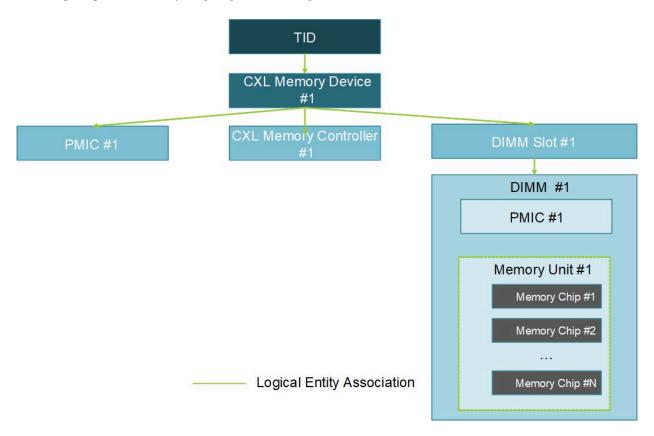

Figure 8 illustrates the model which is used in the examples.

Figure 8 — Example model diagrams

# 8.1 Model hierarchy

The model PDRs identify the elements depicted in Figure 6. The hierarchies are illustrated in the following diagram. For simplicity, Figure 9 and Figure 10 does not show the associated sensors.

Figure 9 — CMB — Model hierarchy

Figure 10 — CMM — Model hierarchy

# 8.2 Top-level TID

The terminus ID is identified by the terminus locator PDR. The TID defines the top-level entry point to the PLDM model. Because there is only one CXL Memory Controller on the CXL Memory Device in this example, there is only one TID.

| Field name          | Value | Description                       |  |

|---------------------|-------|-----------------------------------|--|

| ContainerID         | 0     | System                            |  |

| TID                 |       | Assigned by MC                    |  |

| RecordHandle        | 10    | Opaque number                     |  |

| TerminusLocatorSize | 1     | Size of (EID) or size of (UID)    |  |

| TerminusLocatorType | 1     | MCTP EID                          |  |

| EID                 | EID   | MCTP assigned EID Value           |  |

| UID                 | UID   | Vendor provided UUID format value |  |

Table 3 — TID PDR

The TID value is assigned to the terminus by the MC. When the transport layer is MCTP, the identification of the terminus is performed using the Endpoint ID (EID) value. The UID value in the terminus

locator PDR uses the device UUID value as the terminus UID. For more information regarding terminus locator PDR see DSP0248

# 8.3 CXL Memory Device Model

The top level of the model is the CXL Memory Device. The CXL Memory Device includes the physical elements which include CXL Memory Controller (only one CXL Memory Controller in this example) and a PMIC and memory chips (2 memory chips in this example).

Figure 11 — CMB level elements

The sensors on the CXL Memory Device level are described using a reference to the measured entity, independent of the container that includes all the physical elements on the CXL Memory Device.

**Table 4 — CMB Container PDR**

| Container Entity — CXL Memory Board 1     |     |

|-------------------------------------------|-----|

| ContainerID                               | 100 |

| CXL Memory Board — Entity Association PDR |     |

| EntityType                                   | 65                               | Memory Board          |

|----------------------------------------------|----------------------------------|-----------------------|

| EntityInstanceNumber                         | 1                                |                       |

| ContainerID                                  | 0                                | System                |

| AssociationType                              | Physical to Physical containment |                       |

| Contained Entity 1 — CXL Memory Controller 1 |                                  |                       |

| EntityType                                   | 143                              | CXL Memory Controller |

| EntityInstanceNumber                         | 1                                |                       |

| ContainerID                                  | 100                              | CXL Memory Board 1    |

| Contained Entity 2 — PMIC 1                  |                                  |                       |

| EntityType                                   | 124                              | DC-DC converter       |

| EntityInstanceNumber                         | 1                                |                       |

| ContainerID                                  | 100                              | CXL Memory Board 1    |

| Contained Entity 3 — Memory Slot 1           |                                  |                       |

| EntityType                                   | 186                              | Slot                  |

| EntityInstanceNumber                         | 1                                |                       |

| ContainerID                                  | 100                              | CXL Memory Board 1    |

|                                              |                                  |                       |

Figure 12 — CMM level elements

**Table 5 — CMM Container PDR**

| CXL Memory Module — Entity Association PDR   |                                  |                       |

|----------------------------------------------|----------------------------------|-----------------------|

| ContainerID                                  |                                  | 100                   |

| Container Entity — CXL Memory Module 1       |                                  |                       |

| EntityType                                   | 66                               | Memory Module         |

| EntityInstanceNumber                         | 1                                |                       |

| ContainerID                                  | 0                                | System                |

| AssociationType                              | Physical to Physical containment |                       |

| Contained Entity 1 — CXL Memory Controller 1 |                                  |                       |

| EntityType                                   | 143                              | CXL Memory Controller |

| EntityInstanceNumber                         | 1                                |                       |

| ContainerID                                  | 100                              | CXL Memory Module 1   |

| Contained Entity 2 — PMIC 1                  |                                  |                       |

| EntityType                                   | 124                              | DC-DC converter       |

| EntityInstanceNumber                         | 1                                |                       |

| ContainerID                                  | 100                              | CXL Memory Module 1   |

| Contained Entity 3 — Memory Media 1          |                                  |                       |

| EntityType                                   | 142                              | Memory Chip           |

| EntityInstanceNumber                         | 1                                |                       |

| ContainerID                                  | 100                              | CXL Memory Module 1   |

| Contained Entity 3 — Memory Media 2          |                                  |                       |

| EntityType                                   | 142                              | Memory Chip           |

| EntityInstanceNumber                         | 2                                |                       |

| ContainerID                                  | 100                              | CXL Memory Module 1   |

|                                              |                                  |                       |

Note that the CXL Memory Device container ID, 100, is referenced by the sensors not included in the

entity association PDR. The enumeration model shown in Figure 7 includes the container ID for every hierarchy level.

## 8.3.1 CXL Memory Device Temperature Sensor PDR

**Table 6 — CMD Ambient Temperature Sensor PDR**

| CXL Memory Device — Temperature Sensor PDR |         |                               |

|--------------------------------------------|---------|-------------------------------|

| Field                                      | Value   | Description                   |

| RecordHandle                               | 1100    |                               |

| SensorID                                   | 1       |                               |

| EntityType                                 | 65 / 66 | Memory Board / Memory Module  |

| EntityInstance                             | 1       | CXL Memory Device Instance #1 |

| ContainerID                                | 0       | System                        |

| BaseUnit                                   | 2       | Degrees C                     |

| UnitModifier                               | 0       | No need for scaling           |

# **8.3.2 CXL Memory Device Power Sensor PDR**

**Table 7 — CMD Power Sensor PDR**

| CXL Memory Device — Power Sensor PDR |         |                               |

|--------------------------------------|---------|-------------------------------|

| Field                                | Value   | Description                   |

| RecordHandle                         | 1101    |                               |

| SensorID                             | 2       |                               |

| EntityType                           | 65 / 66 | Memory Board / Memory Module  |

| EntityInstance                       | 1       | CXL Memory Device Instance #1 |

| ContainerID                          | 0       | System                        |

| BaseUnit                             | 7       | Watt                          |

| UnitModifier                         | -1      | 0.1 Watt resolution           |

# 8.3.3 CXL Memory Device Composite State Sensor PDR

Table 8 — CMD Composite State Sensor PDR

| CXL Memory Device composite state sensor PDR |                             |                               |

|----------------------------------------------|-----------------------------|-------------------------------|

| Field                                        | Value                       | Description                   |

| RecordHandle                                 | 1102                        |                               |

| SensorID                                     | 3                           |                               |

| EntityType                                   | 65 / 66                     | Memory Board / Memory Module  |

| EntityInstance                               | 1                           | CXL Memory Device Instance #1 |

| ContainerID                                  | 0                           | System                        |

| CompositeSensorCount                         | 3                           |                               |

| SensorType                                   | 21                          | Thermal Trip                  |

| PossibleStates                               | Refer to Table 1 of DSP0249 |                               |

| SensorType                                   | 1                           | Health state                  |

| PossibleStates                               | Refer to Table 1 of DSP0249 |                               |

| SensorType                                   | 10                          | Operational Fault Status      |

| PossibleStates                               | Refer to Table 1 of DSP0249 |                               |

|                                              |                             |                               |

# 8.3.4 CXL Memory Device Aggregated Temperature Sensor PDR

Table 9 — CMD Aggregated Temperature Sensor PDR

| CXL Memory Device — Aggregated Sensor PDR |       |             |

|-------------------------------------------|-------|-------------|

| Field                                     | Value | Description |

| RecordHandle                              | 1103  |             |

| SensorID                                  | 4     |             |

| CXL Memory Device — Aggregated Sensor PDR |         |                               |

|-------------------------------------------|---------|-------------------------------|

| EntityType                                | 65 / 66 | Memory Board / Memory Module  |

| EntityInstance                            | 1       | CXL Memory Device Instance #1 |

| ContainerID                               | 0       | System                        |

| BaseUnit                                  | 2       | Degrees C                     |

| UnitModifier                              | 0       | No need for scaling           |

# 8.3.5 CXL Memory Device Thermal Throttle Enable Effecter PDR

**Table 10 — CMD Thermal Throttle Enable Effecter PDR**

| CXL Memory Device — Thermal Throttle Enable Effecter PDR |                             |                                 |

|----------------------------------------------------------|-----------------------------|---------------------------------|

| Field                                                    | Value                       | Description                     |

| RecordHandle                                             | 1104                        |                                 |

| SensorID                                                 | 5                           |                                 |

| EntityType                                               | 65 / 66                     | Memory Board / Memory<br>Module |

| EntityInstance                                           | 1                           | CXL Memory Device Instance #1   |

| ContainerID                                              | 0                           | System                          |

| SensorType                                               | 14                          | Performance                     |

| PossibleStates                                           | Refer to Table 1 of DSP0249 |                                 |

# 8.3.6 CXL Memory Device Power Throttle Enable Effecter PDR

**Table 11 — CMD Power Throttle Enable Effecter PDR**

|   | CXL Memory Device — Power Throttle Enable Effecter PDR |       |             |

|---|--------------------------------------------------------|-------|-------------|

| F | ield                                                   | Value | Description |

| CXL Memory Device — Power Throttle Enable Effecter PDR |                             |                                 |

|--------------------------------------------------------|-----------------------------|---------------------------------|

| RecordHandle                                           | 1105                        |                                 |

| SensorID                                               | 6                           |                                 |

| EntityType                                             | 65 / 66                     | Memory Board / Memory<br>Module |

| EntityInstance                                         | 1                           | CXL Memory Device Instance #1   |

| ContainerID                                            | 0                           | System                          |

| SensorType                                             | 14                          | Performance                     |

| PossibleStates                                         | Refer to Table 1 of DSP0249 |                                 |

# **8.4 CXL Memory Controller Model**

The CXL Memory controller is the active device in charge of providing host-access to its attached memory using CXL semantics. Being a physical entity, the CXL Memory controller is already declared within Figure 7. The content of the CXL Memory controller includes a set of device-level sensors. The following diagram illustrates the model elements for the CXL Memory controller in the example model:

Figure 13 — Example model CXL Memory Controller

The CXL Memory controller content is declared using an entity-association PDR that includes the hierarchical description of the CXL Memory controller. The device-level sensors are declared with separate PDRs using direct references to the measured entities.

Table 12 — CXL Memory Controller Entity Association PDR

| CXL Memory Controller — Entity Association PDR |  |  |

|------------------------------------------------|--|--|

|------------------------------------------------|--|--|

| ContainerID                                |                                  | 200               |

|--------------------------------------------|----------------------------------|-------------------|

| Container Entity — CXL Memory Controller 1 |                                  |                   |

| EntityType                                 | 143                              | Memory Controller |

| EntityInstance Number                      | 1                                |                   |

| ContainerID                                | 100                              | CMB #1 / CMM #1   |

|                                            |                                  |                   |

| AssociationType                            | Physical to Physical containment |                   |

## 8.4.1 CXL Memory Controller Temperature Sensor PDR

**Table 13 — CXL Memory Controller Temperature Sensor PDR**

| CXL Memory Controller — Temperature Sensor PDR |       |                     |

|------------------------------------------------|-------|---------------------|

| Field                                          | Value | Description         |

| RecordHandle                                   | 2100  |                     |

| SensorID                                       | 10    |                     |

| EntityType                                     | 143   | Memory Controller   |

| EntityInstance                                 | 1     |                     |

| ContainerID                                    | 100   | CMB #1 / CMM #1     |

| BaseUnit                                       | 2     | Degrees C           |

| UnitModifier                                   | 0     | No need for scaling |

# **8.4.2 CXL Memory Controller Power Sensor PDR**

Table 14 — CXL Memory Controller Power Sensor PDR

| CXL Memory Controller — Power Sensor PDR |       |             |

|------------------------------------------|-------|-------------|

| Field                                    | Value | Description |

| RecordHandle                             | 2200  |             |

| SensorID                                 | 20    |             |

| CXL Memory Controller — Power Sensor PDR |     |                     |

|------------------------------------------|-----|---------------------|

| EntityType                               | 143 | Memory Controller   |

| EntityInstance                           | 1   |                     |

| ContainerID                              | 100 | CMB #1 / CMM #1     |

| BaseUnit                                 | 7   | Watt                |

| UnitModifier                             | -1  | 0.1 Watt resolution |

#### **8.5 PMIC**

The power management IC (or voltage regulator) regulates power for the CXL memory controllers and/ or memory units. Being a physical entity, the PMIC is already declared within Figure 7. The content of the PMIC includes a set of device-level sensors. The following diagram illustrates the model elements for the PMIC in the example model:

Figure 14 — Example model PMIC

The PMIC content is declared using an entity-association PDR that includes the hierarchical description of the PMIC. The device-level sensors are declared with separate PDRs using direct references to the measured entities.

**Table 15 — PMIC Entity Association PDR**

| PMIC — Entity Association PDR |     |                 |

|-------------------------------|-----|-----------------|

| ContainerID                   |     | 300 / 600       |

| ContainerEntity — PMIC 1      |     |                 |

| EntityType                    | 124 | DC-DC converter |

| EntityInstanceNumber          | 1   |                 |

| ContainerID     | 100/400                          | CMB #1 / CMM #1 or DIMM #1 |

|-----------------|----------------------------------|----------------------------|

|                 |                                  |                            |

| AssociationType | Physical to Physical containment |                            |

# **8.5.1 PMIC Temperature Sensor PDR**

**Table 16 — PMIC Temperature Sensor PDR**

| PMIC — Temperature Sensor PDR |           |                            |

|-------------------------------|-----------|----------------------------|

| Field                         | Value     | Description                |

| RecordHandle                  | 3100/7100 |                            |

| SensorID                      | 100       |                            |

| EntityType                    | 124       | DC-DC converter            |

| EntityInstance                | 1         |                            |

| ContainerID                   | 100/400   | CMB #1 / CMM #1 or DIMM #1 |

| BaseUnit                      | 2         | Degrees C                  |

| UnitModifier                  | 0         | No need for scaling        |

#### **8.5.2 PMIC Power Sensor PDR**

**Table 17 — PMIC Power Sensor PDR**

| PMIC — Power Sensor PDR |           |                            |

|-------------------------|-----------|----------------------------|

| Field                   | Value     | Description                |

| RecordHandle            | 3200/8200 |                            |

| SensorID                | 200       |                            |

| EntityType              | 124       | DC-DC converter            |

| EntityInstance          | 1         |                            |

| ContainerID             | 100/400   | CMB #1 / CMM #1 or DIMM #1 |

| BaseUnit                | 7         | Watt                       |

| PMIC — Power Sensor PDR |    |                     |

|-------------------------|----|---------------------|

| UnitModifier            | -1 | 0.1 Watt resolution |

#### **8.5.3 PMIC Current Sensor PDR**

**Table 18 — PMIC Current Sensor PDR**

| PMIC — Current Sensor PDR |           |                            |

|---------------------------|-----------|----------------------------|

| Field                     | Value     | Description                |

| RecordHandle              | 3300/9300 |                            |

| SensorID                  | 300       |                            |

| EntityType                | 124       | DC-DC converter            |

| EntityInstance            | 1         |                            |

| ContainerID               | 100/400   | CMB #1 / CMM #1 or DIMM #1 |

| BaseUnit                  | 6         | Amps                       |

| UnitModifier              | 0         | No need for scaling        |

#### 8.5.4 PMIC Fault Sensor PDR

**Table 19 — PMIC Fault Sensor PDR**

| PMIC — Fault Sensor PDR |                             |                            |

|-------------------------|-----------------------------|----------------------------|

| Field                   | Value                       | Description                |

| RecordHandle            | 3400/10400                  |                            |

| SensorID                | 400                         |                            |

| EntityType              | 124                         | DC-DC converter            |

| EntityInstance          | 1                           |                            |

| ContainerID             | 100/400                     | CMB #1 / CMM #1 or DIMM #1 |

| SensorType              | 256                         | Power Supply State         |

| PossibleStates          | Refer to Table 1 of DSP0249 |                            |

#### 8.6 DIMM Slot

The DIMM Slot refers to the empty slots or sockets mounted on the CMB PCB that allows to insert DIMM. Being a physical entity, the DIMM Slot is already declared within Figure 7. The content of the DIMM Slot includes a set of device-level sensors. The following diagram illustrates the model elements for the DIMM Slot in the example model:

Figure 15 — Example model DIMM Slot

The DIMM Slot content is declared using an entity-association PDR that includes the hierarchical description of the DIMM Slot. The device-level sensors are declared with separate PDRs using direct references to the measured entities.

Table 20 — DIMM Slot Entity Association PDR

| Memory Slot — Entity Association PDR |                                  |        |

|--------------------------------------|----------------------------------|--------|

| ContainerID                          |                                  | 400    |

| Container Entity — DIMM Slot 1       |                                  |        |

| EntityType                           | 186                              | Slot   |

| EntityInstance Number                | 1                                |        |

| ContainerID                          | 100                              | CMB #1 |

|                                      |                                  |        |

| AssociationType                      | Physical to Physical containment |        |

#### **8.6.1 DIMM Presence Sensor PDR**

Table 21 — DIMM Presence Sensor PDR

| DIMM Presence Sensor PDR |                             |             |

|--------------------------|-----------------------------|-------------|

| Field                    | Value                       | Description |

| RecordHandle             | 4100                        |             |

| SensorID                 | 500                         |             |

| EntityType               | 186                         | Slot        |

| EntityInstance           | 1                           |             |

| ContainerID              | 100                         | CMB #1      |

| SensorType               | 13                          | Presence    |

| PossibleStates           | Refer to Table 1 of DSP0249 |             |

#### **8.7 DIMM**