| Document Identifier: DSP1071 | 3 |

|------------------------------|---|

| Date: 2017-01-19             | 4 |

| Version: 1.0.0               | 5 |

|                              |   |

# 6 Multi-type System Memory Profile

7 Supersedes: None

1

- 8 Document Class: Normative

- 9 Document Status: Published

- 10 Document Language: en-US

#### 11 Copyright Notice

12 Copyright © 2017 Distributed Management Task Force, Inc. (DMTF). All rights reserved.

DMTF is a not-for-profit association of industry members dedicated to promoting enterprise and systems management and interoperability. Members and non-members may reproduce DMTF specifications and documents, provided that correct attribution is given. As DMTF specifications may be revised from time to time, the particular version and release date should always be noted.

17 Implementation of certain elements of this standard or proposed standard may be subject to third party

18 patent rights, including provisional patent rights (herein "patent rights"). DMTF makes no representations

- to users of the standard as to the existence of such rights, and is not responsible to recognize, disclose, or identify any or all such third party patent right, owners or claimants, nor for any incomplete or

- 20 or identify any or all such third party patent right, owners or claimants, nor for any incomplete or 21 inaccurate identification or disclosure of such rights, owners or claimants. DMTF shall have no liability to

any party, in any manner or circumstance, under any legal theory whatsoever, for failure to recognize,

disclose, or identify any such third party patent rights, or for such party's reliance on the standard or

24 incorporation thereof in its product, protocols or testing procedures. DMTF shall have no liability to any

25 party implementing such standard, whether such implementation is foreseeable or not, nor to any patent

26 owner or claimant, and shall have no liability or responsibility for costs or losses incurred if a standard is

27 withdrawn or modified after publication, and shall be indemnified and held harmless by any party

implementing the standard from any and all claims of infringement by a patent owner for such

29 implementations.

30 For information about patents held by third-parties which have notified the DMTF that, in their opinion,

- 31 such patent may relate to or impact implementations of DMTF standards, visit

- 32 <u>http://www.dmtf.org/about/policies/disclosures.php</u>.

- 33 This document's normative language is English. Translation into other languages is permitted.

## Contents

| 36       | Fore  | eword.  |                                                                    | . 6 |

|----------|-------|---------|--------------------------------------------------------------------|-----|

| 37       | Intro | oductio | n                                                                  | .7  |

| 38       | 1     | Scope   | 9                                                                  | . 8 |

| 39       | 2     | Norm    | ative references                                                   | . 8 |

| 40       | 3     |         | s and definitions                                                  |     |

| 41       | 4     |         | ols and abbreviated terms                                          |     |

| 42       | 5     |         | Disis                                                              |     |

|          |       |         |                                                                    |     |

| 43       | 6     |         | iption                                                             |     |

| 44       | 7     |         | mentation                                                          |     |

| 45<br>46 |       | 7.1     | Representing raw memory                                            |     |

| 46<br>47 |       | 7.2     | Representing visible memory<br>7.2.1 CIM_VisibleMemory.HealthState |     |

| 47<br>48 |       |         | 7.2.2 CIM_VisibleMemory.EnabledState                               |     |

| 40<br>49 |       |         | 7.2.2 CIM_VISIBleViendry.EnabledState                              |     |

| 49<br>50 |       |         | 7.2.3 Representing memory size                                     |     |

| 51       |       |         | 7.2.5 CIM_VisibleMemory.Replication                                |     |

| 52       |       | 7.3     | Representing topology                                              |     |

| 53       |       | 7.0     | 7.3.1 CIM_MemoryController                                         |     |

| 54       |       |         | 7.3.2 CIM_Processor                                                |     |

| 55       |       |         | 7.3.3 Representing non-uniform memory access configurations        |     |

| 56       |       | 7.4     | Representing memory configuration                                  |     |

| 57       | 8     | Metho   | pds                                                                |     |

| 58       | •     | 8.1     | CIM_VisibleMemory                                                  |     |

| 59       |       | 8.2     | CIM_RawMemory                                                      |     |

| 60       |       | 8.3     | CIM_MemoryController                                               |     |

| 61       |       | 8.4     | CIM_Processor                                                      |     |

| 62       |       | 8.5     | CIM_ConcreteDependency                                             | 17  |

| 63       |       | 8.6     | CIM_AssociatedMemory                                               |     |

| 64       |       | 8.7     | CIM_BasedOn                                                        | 18  |

| 65       | 9     | Use c   | ases                                                               | 18  |

| 66       |       | 9.1     | Advertising profile conformance                                    | 18  |

| 67       |       | 9.2     | Single visible memory extent                                       | 19  |

| 68       |       | 9.3     | Two visible memory extents                                         |     |

| 69       |       | 9.4     | Uniform memory access extents                                      |     |

| 70       |       | 9.5     | Non-Uniform Memory Access (NUMA) extents                           |     |

| 71       |       | 9.6     | Determine persistent memory capacity                               |     |

| 72       |       | 9.7     | Determine total installed memory capacity                          |     |

| 73       |       | 9.8     | Determine capacity by processor affinity                           |     |

| 74       |       | 9.9     | Determine processor affinity for visible memory                    |     |

| 75       | 10    |         | Elements                                                           |     |

| 76       |       | 10.1    | CIM_RegisteredProfile                                              |     |

| 77       |       | 10.2    | CIM_VisibleMemory                                                  |     |

| 78       |       | 10.3    | CIM_RawMemory                                                      |     |

| 79       |       | 10.4    | CIM_MemoryController                                               |     |

| 80       |       | 10.5    | CIM_Processor                                                      |     |

| 81       |       | 10.6    | CIM_ConcreteDependency                                             |     |

| 82<br>83 |       | 10.7    | CIM_SystemDevice                                                   |     |

| 83<br>84 |       |         | 10.7.1 Relating CIM_Processor to CIM_ComputerSystem                |     |

| 85       |       | 10.8    | CIM_AssociatedMemory                                               |     |

| 50       |       |         |                                                                    | - · |

| 86 | 10.9 CIM Based | On                                | . 27 |

|----|----------------|-----------------------------------|------|

|    |                | SNIA Memory Configuration Profile |      |

|    | · · ·          | Change log                        |      |

|    |                |                                   |      |

# 90 Figures

| 91 | Figure 1 – Multi-type System Memory: Class diagram        | . 12 |

|----|-----------------------------------------------------------|------|

| 92 | Figure 2 – Registered Profile object diagram              | . 18 |

| 93 | Figure 3 – Single visible memory extent object diagram    | . 19 |

| 94 | Figure 4 – Distinct visible memory extents object diagram |      |

| 95 | Figure 5 – UMA configuration object diagram               |      |

| 96 | Figure 6 – NUMA configuration object diagram              | . 22 |

| 97 | Figure 7 – Memory Configuration Profile                   | . 28 |

|    |                                                           |      |

#### 98

## 99 Tables

| 100 | Table 1 – Related profiles                                |    |

|-----|-----------------------------------------------------------|----|

| 101 | Table 2 – Operations: CIM_VisibleMemory                   |    |

| 102 | Table 3 – Operations: CIM_RawMemory                       |    |

| 103 | Table 4 – Operations: CIM_MemoryController                |    |

| 104 | Table 5 – Operations: CIM_Processor                       |    |

| 105 | Table 6 – Operations: CIM_ConcreteDependency              |    |

| 106 | Table 7 – Operations: CIM_AssociatedMemory                |    |

| 107 | Table 8 – Operations: CIM_BasedOn                         |    |

| 108 | Table 9 – CIM Elements – Multi-type System Memory Profile |    |

| 109 | Table 10 – Class: CIM_RegisteredProfile                   |    |

| 110 | Table 11 – Class: CIM_VisibleMemory                       | 24 |

| 111 | Table 12 – Class: CIM_RawMemory                           | 24 |

| 112 | Table 13 – Class: CIM_MemoryController                    |    |

| 113 | Table 14 – Class: CIM_Processor                           |    |

| 114 | Table 15 – Class: CIM_ConcreteDependency                  |    |

| 115 | Table 16 – Class: CIM_SystemDevice – use 1                |    |

| 116 | Table 17 – Class: CIM_SystemDevice – use 2                |    |

| 117 | Table 18 – Class: CIM_AssociatedMemory                    |    |

| 118 | Table 19 – Class: CIM_BasedOn                             |    |

|     |                                                           |    |

119

# 121 Foreword

- 122 The *Multi-type System Memory Profile* (DSP1071) was prepared by the CIM Profiles for Platforms and 123 Services Working Group.

- 124 DMTF is a not-for-profit association of industry members dedicated to promoting enterprise and systems 125 management and interoperability.

#### 126 Acknowledgments

- 127 The DMTF acknowledges the following individuals for their contributions to this document:

- 128 Editor:

- Scott Kirvan Intel

- 130 Contributors:

- Paul von Behren Intel

- 132 Barbara Craig Hewlett-Packard

- 133 John Leung Intel

- 134

- 135

# Introduction

This specification describes a management profile including the CIM model and associated behavior for

computer system memory. Specifically, it addresses uni- and multi-processor systems with one or more

individually managed memory extents.

140 The information in this specification should be sufficient for a provider or consumer of this data to

unambiguously identify the classes, properties, methods, and values that shall be instantiated to

subscribe, advertise, produce, or consume an indication using the DMTF Common Information Model

143 (CIM) Schema.

144 The target audience for this specification is implementers who are writing CIM-based providers or 145 consumers of management interfaces that represent the components described in this document.

# **Multi-type System Memory Profile**

#### 147 **1 Scope**

148 The Multi-type System Memory Profile extends the management capabilities of referencing profiles by 149 adding the ability to detect and monitor individual memory extents in a computer system. Logical memory

extents are modeled in the context of related profiles including those that: 1) model the memory's physical aspects; 2) identify the hosting system; 3) allow for configuration; and 4) define registration information.

151 aspects; 2) identify the hosting system; 3) allow for configuration; and 4) define registration informatio 152 This profile would generally be used instead of the System Memory Profile (DSP1026) rather than in

153 conjunction with it.

## 154 **2 Normative references**

- 155 The following referenced documents are indispensable for the application of this document. For dated or

- versioned references, only the edition cited (including any corrigenda or DMTF update versions) applies.

- 157 For references without a date or version, the latest published edition of the referenced document

- 158 (including any corrigenda or DMTF update versions) applies.

- 159 DMTF DSP0004, *CIM Infrastructure Specification 2.7*,

- 160 <u>http://www.dmtf.org/standards/published\_documents/DSP0004\_2.7.pdf</u>

- 161 DMTF DSP0215, Server Management Managed Element Addressing Specification 1.0, 162 http://www.dmtf.org/standards/published\_documents/DSP0215\_1.0.pdf

- 163 DMTF DSP0223, Generic Operations 1.0,

164 <u>http://www.dmtf.org/standards/published\_documents/DSP0223\_1.0.pdf</u>

- 165 DMTF DSP0228, Message Registry XML Schema 1.0,

- 166 <u>http://schemas.dmtf.org/wbem/messageregistry/1/dsp0228\_1.0.1.xsd</u>

- 167 DMTF DSP1001, *Management Profile Specification Usage Guide 1.1*, 168 http://www.dmtf.org/standards/published\_documents/DSP1001\_1.1.pdf

- 169 DMTF DSP1033, Profile Registration Profile 1.1,

- 170 <u>http://dmtf.org/sites/default/files/standards/documents/DSP1033\_1.1.0.pdf</u>

- 171 DMTF DSP1011, Physical Asset Profile

- 172 <u>http://dmtf.org/sites/default/files/standards/documents/DSP1011\_1.0.2.pdf</u>

- 173 DMTF DSP1022, CPU Profile

- 174 <u>http://dmtf.org/sites/default/files/standards/documents/DSP1022\_1.0.1.pdf</u>

- 175 DMTF DSP8016, WBEM Operations Message Registry 1.0,

- 176 <u>http://schemas.dmtf.org/wbem/messageregistry/1/dsp8016\_1.0.xml</u>

- 177 DMTF DSP8020, Standard Metrics Schema 1.0,

- 178 <u>http://schemas.dmtf.org/wbem/metricregistry/1/dsp8020\_1.0.xsd</u>

- 179 IETF RFC5234, ABNF: Augmented BNF for Syntax Specifications, January 2008,

- 180 <u>http://tools.ietf.org/html/rfc5234</u>

| 181<br>182               | ISO/IEC Directives, Part 2, Rules for the structure and drafting of International Standards,<br>http://isotc.iso.org/livelink/livelink.exe?func=ll&objId=4230456&objAction=browse&sort=subtype |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 183<br>184               | The Open Group, "Regular Expressions" in <i>The Single UNIX</i> ® <i>Specification, Version</i> 2, <u>http://www.opengroup.org/onlinepubs/7908799/xbd/re.html</u>                              |

| 185                      | 3 Terms and definitions                                                                                                                                                                        |

| 186<br>187               | 3.1<br>can                                                                                                                                                                                     |

| 188                      | used for statements of possibility and capability, whether material, physical, or causal                                                                                                       |

| 189<br>190               | 3.2<br>cannot                                                                                                                                                                                  |

| 191                      | used for statements of possibility and capability, whether material, physical, or causal                                                                                                       |

| 192<br>193<br>194<br>195 | <ul> <li>3.3</li> <li>conditional</li> <li>used to indicate requirements strictly to be followed, in order to conform to the document when the specified conditions are met</li> </ul>         |

| 196                      | 3.4                                                                                                                                                                                            |

| 197<br>198<br>199        | mandatory<br>used to indicate requirements strictly to be followed, in order to conform to the document and from which<br>no deviation is permitted                                            |

| 200                      | 3.5                                                                                                                                                                                            |

| 201<br>202               | may<br>used to indicate a course of action permissible within the limits of the document                                                                                                       |

| 203                      | 3.6                                                                                                                                                                                            |

| 204<br>205               | memory extent<br>used generically to indicate a range of memory addresses that can participate in management operations                                                                        |

| 206<br>207               | 3.7<br>memory module                                                                                                                                                                           |

| 208                      | non-technology specific term for a circuit board hosting memory integrated circuits                                                                                                            |

| 209<br>210               | 3.8<br>need not                                                                                                                                                                                |

| 211                      | used to indicate a course of action permissible within the limits of the document                                                                                                              |

| 212<br>213<br>214        | <b>3.9</b><br><b>optional</b><br>used to indicate a course of action permissible within the limits of the document                                                                             |

| 215<br>216               | 3.10<br>persistent memory                                                                                                                                                                      |

| 217                      | byte addressable memory which retains its contents across system power cycles                                                                                                                  |

218 **3.11**

#### 219 referencing profile

indicates a profile that owns the definition of a class used, but not defined, in this document and can beincluded in the "Referenced Profiles" table

#### 222 **3.12**

- 223 shall

- used to indicate requirements strictly to be followed, in order to conform to the document and from which no deviation is permitted

- 226 **3.13**

#### shall not

- used to indicate requirements strictly to be followed, in order to conform to the document and from whichno deviation is permitted

- 230 **3.14**

#### 231 should

- used to indicate that among several possibilities, one is recommended as particularly suitable, without

mentioning or excluding others, or that a certain course of action is preferred but not necessarily required

- 234 **3.15**

#### 235 should not

- used to indicate that a certain possibility or course of action is deprecated but not prohibited

- 237 **3.16**

#### 238 unspecified

239 indicates that this profile does not define any constraints for the referenced CIM element or operation

## 240 **4** Symbols and abbreviated terms

- 241 **4.1**

- 242 NUMA

- 243 Non-Uniform Memory Access

- 244 **4.2**

- 245 NVM

- 246 Non-Volatile Memory

- 247 **4.3**

- 248 **PM**

- 249 Persistent Memory

- 250 **4.4**

- 251 QoS

- 252 Quality of Service

- 253 **4.5**

- 254 UMA

- 255 Uniform Memory Access

## 256 **5** Synopsis

- 257 **Profile Name:** *Multi-type System Memory*

- 258 Version: 1.0.0a

- 259 **Organization:** DMTF

- 260 CIM Schema Version: 2.41

- 261 **Central Class:** CIM\_VisibleMemory

- 262 **Scoping Class:** CIM\_ComputerSystem

System memory devices have traditional been physical device whose only purpose was a volatile memory (e.g., DRAM, SRAM, Cache memory). These memory devices have a fixed size. The

- 265 manageability these types of memory is specified in the DSP1026 (System Memory Profile).

- There also exist system memory devices, whose characteristics can be configured. The characteristics

include size, affinity, and quality of service. This type of system memory is called multi-type system

memory.

- 269 The Multi-type Memory Profile extends the management capabilities of the referencing profiles by adding

the capability to represent and manage multiple types of memory within a managed system. The profile

supports systems with one or more memory regions where each region can be individually managed.

- Table 1 identifies profiles on which this profile has a dependency.

- 273 CIM\_VisibleMemory shall be the Central Class of this profile.

- 274 CIM ComputerSystem shall be the Scoping Class of this profile. The instance of CIM ComputerSystem

- with which the Central Instance is associated through an instance of CIM\_SystemDevice shall be the

- 276 Scoping Instance of this profile.

- 277

| Profile Name                 | Organization | Version | Relationship |

|------------------------------|--------------|---------|--------------|

| Physical Asset               | DMTF         | 1.0.2   | Mandatory    |

| Profile Registration         | DMTF         | 1.1.0   | Mandatory    |

| CPU                          | DMTF         | 1.0.1   | Conditional  |

| Memory Configuration Profile | SNIA         | 1.0.0a  | Conditional  |

#### Table 1 – Related profiles

#### 278 6 **Description**

- The Multi-type System Memory Profile describes the elements which allow multiple types of memory to be represented and managed.

- This profile can be used to manage the following capabilities of memory regions in a system with multiple types of memory.

- A memory region can have specific quality of service (QoS) characteristics, such a persistence, redundancy, block access.

- A memory region can be configured from a pool of raw memory.

- A memory region can be visible to, or have affinity with, specific processors and memory controllers.

- A memory region can be visible to one or more processors (shared).

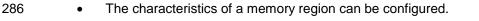

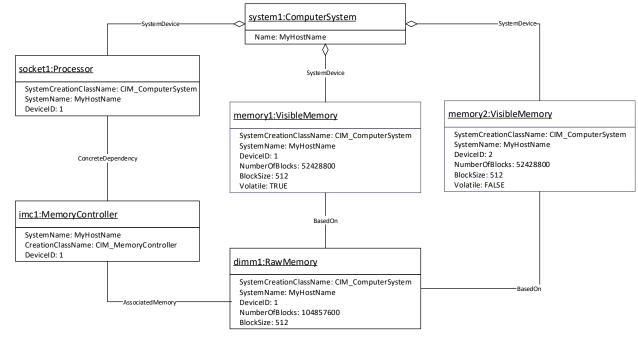

Figure 1 shows the Multi-type System Memory Profile class hierarchy. For simplicity, the prefix CIM\_ has been removed from the names of the classes.

292

#### 293

Figure 1 – Multi-type System Memory: Class diagram

Each memory region visible to the computer system is modeled by an instance of CIM\_VisibleMemory.

295 Each physical memory region is associated with its logical counterpart, a raw memory region. Raw

296 memory is not visible to the computer system. Raw memory is modeled by an instance of

CIM\_RawMemory and its relationship to the visible memory region is modeled by the CIM\_BasedOnassociation.

A memory controller configures raw memory to create the visible memory regions. Memory controllers are represented by instances of CIM\_MemoryController and their relationship to the raw memory region is modeled by the CIM\_AssociatedMemory association.

302 In multi-processor systems, memory extents can have an affinity to a specific processor and memory

303 controller. An affinity relationship between memory and a processor/controller can indicate exclusive or

304 preferential access to the memory by that processor. The Multi-type System Memory Profile models a

305 relationship between raw memory extents and their controller and processor such that a management

application can determine memory affinity and the physical memory topology.

The SNIA Memory Configuration Profile may be used to model memory regions. That profile includes the CIM\_MemoryResources and CIM\_MemoryAllocationSetting elements. The CIM\_ElementSettingData and CIM\_ElementAllocatedFromPool associations are used to model the relationship between the elements of these two profiles.

## 311 **7 Implementation**

312 This clause details the requirements related to the arrangement of instances and their most important

313 properties. Class methods are discussed in clause 8; a comprehensive treatment of properties is left to 314 clause 10.

#### 315 **7.1 Representing raw memory**

- An instance of CIM\_RawMemory shall represent a memory region which is realized by physical memory,

but not visible to the computer system. Instances of CIM\_RawMemory shall be associated with an

instance of CIM\_PhysicalMemory with an instance of CIM\_Realizes.

- 319 There shall be at least one instance of CIM RawMemory.

- 320 If SMBIOS structure table models a memory device (Type 17), then CIM\_RawMemory instance shall

- 321 correspond to a structure in the SMBIOS table. For a corresponding memory device, the values of the

- BlockSize and NumberOfBlocks properties of the CIM\_RawMemory instance shall be equal to the values

- in the corresponding SMBIOS Memory Device (Type 17) structure.

#### 324 **7.2 Representing visible memory**

- 325 An instance of CIM\_VisibleMemory shall represent a memory region which is visible to the computer

- system. Instances of CIM\_VisibleMemory shall be associated with the instance of CIM\_ComputerSystem

with an instance of CIM\_SystemDevice.

- 328 There shall be at least one instance of CIM\_VisbileMemory. Additional instances of CIM\_VisibleMemory

- may exist when the system contains more than one memory region with distinct memory characteristics.

For example, one instance may exist for volatile memory and one for non-volatile memory.

- 331 Each instance of CIM\_VisibleMemory shall be associated with one or more instances of

- 332 CIM\_RawMemory, using the CIM\_BasedOn association.

#### 333 **7.2.1 CIM\_VisibleMemory.HealthState**

The CIM\_VisibleMemory.HealthState property may have the values 0 (Unknown), 1 (OK) or 2 (Degraded).

#### 336 **7.2.2 CIM\_VisibleMemory.EnabledState**

- The CIM\_VisibleMemory.EnabledState property shall have a value of 2 (Enabled) when the visible memory that it represents is visible to the computer system to which it's scoped.

- The CIM\_VisibleMemory.EnabledState property shall have a value of 3 (Disabled) when the visible memory, that it represents, is not visible to the computer system to which it's scoped.

#### 341 **7.2.3 Representing memory size**

- The value of the CIM\_VisibleMemory.BlockSize and the CIM\_VisibleMemory.NumberOfBlocks properties shall represent the capacity of the memory region visible to the computer system.

- The capacity, so represented, shall be the visible (or usable) capacity of the underlying memory extent. For example, memory controllers may support a mirroring feature which has the effect of cutting in half

346 the capacity that is usable by the system. The NumberOfBlocks and BlockSize values shall always take 347 into account (i.e., do not include) space utilized for replication, metadata or the like.

#### 348 7.2.4 CIM\_VisibleMemory.AccessGranularity

The CIM\_VisibleMemory.AccessGranularity property shall have a value of 1 (Block Addressable) when the modeled memory region is accessed as a block device. When the memory region is accessed using load and store memory operations the value of CIM\_VisibleMemory.AccessGranularity shall be 2 (Byte Addressable). Vendor unique access mechanisms may be represented by values in the vendor reserved range of 32768..65535.

When the access granularity of a memory device modeled by an instance of CIM\_VisibleMemory is not known, then CIM\_VisibleMemory.AccessGranularity shall be set to 0 (Unknown)."

#### 356 **7.2.5 CIM\_VisibleMemory.Replication**

The CIM\_VisibleMemory.Replication property shall indicate whether the contents of the memory region are replicated. The default value for this property shall be 1 (Not Replicated). If the contents are replicated using resources on the local server the value used shall be 2 (Local Replication). If the replicated region exists on a different server (e.g., using RDMA or the like) the value shall be 3 (Remote Replication). Vendor specific replication mechanisms may be represented by values in the vendor reserved range of 32768..65535.

#### 363 **7.3 Representing topology**

Multi-processor systems are common. Often such systems use a Non-Uniform Memory Access (NUMA) configuration in which memory has an "affinity" to a specific processor. In such a system, memory can be accessed optimally by a processor to which it has an affinity; it is more costly (often drastically so) to access from other processors.

368 In addition to optimal and non-optimal access paths, the topology of memory devices within a system can 369 limit the system's configuration options. For example a given memory controller may support mirroring 370 between memory address ranges of memory modules under its control. In this case it would be important 371 to understand which memory modules are associated with specific memory controllers. A second 372 example of the importance of topology involves memory interleaving. Memory controllers can enhance 373 overall memory performance by interleaving capacity from multiple memory modules. In a NUMA system 374 it could be advantageous to restrict interleaving to those memory modules with affinity to a specific 375 processor. In this case it would be important to understand the affinity of memory modules for a given 376 processor.

In a uniprocessor system all memory is accessed by a single processor. Conformant implementations

include topology information in this degenerate case to minimize special cases for clients attempting to

discover memory topology.

#### 380 **7.3.1 CIM\_MemoryController**

- 381 There may be an instance of CIM\_MemoryContoller.

- 382 When an instance of CIM\_MemoryController exists, it shall be associated to an instance of

- 383 CIM\_RawMemory, which represents raw memory that the memory controller can make available to the 384 computer system, with an instance of CIM AssociatedMemory.

#### 385 **7.3.2 CIM\_Processor**

There may be an instance of CIM\_Processor, which represents a processor with access to managed memory regions. CIM\_Processor instances utilized in this way may be those created by an

- implementation of the CPU Profile. This is the preferred model. Optionally, CIM\_Processor instances may

be created specifically for the Multi-type System Memory Profile.

- 390 When an instance of CIM\_Processor exists, it shall be associated to the instance of

- 391 CIM\_ComputerSystem, to which the memory is visible, with an instance of CIM\_SystemDevice.

#### 392 **7.3.3** Representing non-uniform memory access configurations

- The instances of CIM\_Processor shall be associated to one or more instances of CIM\_MemoryController with an instance of CIM\_ConcreteDependency.

- The instances of CIM\_MemoryController shall be associated to one or more instances of CIM\_RawMemory with an instance of CIM\_AssociatedMemory.

- This path from processor to memory controller to raw memory extent describes the NUMA affinity of a given memory extent to a given processor.

- Additionally, the CIM\_VisibleMemory.ProcessorAffinity property may optionally be used to indicate a

- 400 preferential relationship between a memory region and a processor. A NUMA relationship is an example

- 401 of such a preferential relationship. When a NUMA relationship exists between a memory region as

- 402 modeled by a CIM\_VisibleMemory instance and a processor given by CIM\_Processor the

- 403 CIM\_VisibleMemory.ProcessorAffinity property is conditionally set to the DeviceID of the processor

- instance. When no affinity exists or this property is not used it shall be set to an empty string.

- 405 When a memory controller has an exclusive or preferential access relationship with a processor this

- relationship may be represented by setting the CIM\_MemoryController.ProcessorAffinity property to the

- 407 DeviceID of the CIM\_Processor instance. When no such relationship exists or the property is not used the

- 408 CIM\_MemoryController.ProcessorAffinity property shall be set to an empty string.

#### 409 **7.4 Representing memory configuration**

- 410 The Multi-type System Memory Profile models the static configuration of memory within a system. For

- 411 systems that support a configuration process which results in CIM\_VisibleMemory instances this profile

- 412 references the SNIA Memory Configuration Profile, specifically the MemoryAllocationSettings and

- 413 MemoryResources classes and the associations which link them to the Multi-type System Memory Profile.

- 414 See ANNEX A for more information.

#### 415 8 Methods

This clause details the requirements for supporting intrinsic operations for the CIM elements defined by this profile. No extrinsic methods are defined by this profile.

#### 418 **8.1 CIM\_VisibleMemory**

- 419 Conformant implementations of this profile shall support the operations listed in Table 2 for

- 420 CIM\_VisibleMemory. Each operation shall be supported as defined in <u>DSP0200</u>.

- 421

| Operation       | Requirement | Messages |

|-----------------|-------------|----------|

| GetInstance     | Mandatory   | None     |

| Associators     | Mandatory   | None     |

| AssociatorNames | Mandatory   | None     |

| References      | Mandatory   | None     |

| Operation              | Requirement | Messages |

|------------------------|-------------|----------|

| ReferenceNames         | Mandatory   | None     |

| EnumerateInstances     | Mandatory   | None     |

| EnumerateInstanceNames | Mandatory   | None     |

#### 422 8.2 CIM\_RawMemory

423 Conformant implementations of this profile shall support the operations listed in Table 3 for the

424 CIM\_RawMemory class. Each operation shall be supported as defined in <u>DSP0200</u>.

425

#### Table 3 – Operations: CIM\_RawMemory

| Operation              | Requirement | Messages |  |

|------------------------|-------------|----------|--|

| GetInstance            | Mandatory   | None     |  |

| Associators            | Mandatory   | None     |  |

| AssociatorNames        | Mandatory   | None     |  |

| References             | Mandatory   | None     |  |

| ReferenceNames         | Mandatory   | None     |  |

| EnumerateInstances     | Mandatory   | None     |  |

| EnumerateInstanceNames | Mandatory   | None     |  |

#### 426 8.3 CIM\_MemoryController

427 Conformant implementations of this profile shall support the operations listed in Table 4 for the

428 CIM\_MemoryController class. Each operation shall be supported as defined in <u>DSP0200</u>.

429

#### Table 4 – Operations: CIM\_MemoryController

| Operation              | Requirement | Messages |

|------------------------|-------------|----------|

| GetInstance            | Mandatory   | None     |

| Associators            | Mandatory   | None     |

| AssociatorNames        | Mandatory   | None     |

| References             | Mandatory   | None     |

| ReferenceNames         | Mandatory   | None     |

| EnumerateInstances     | Mandatory   | None     |

| EnumerateInstanceNames | Mandatory   | None     |

#### 430 8.4 CIM\_Processor

431 Conformant implementations of this profile shall support the operations listed in Table 5 for the

432 CIM\_memoryController class. Each operation shall be supported as defined in <u>DSP0200</u>.

433

#### Table 5 – Operations: CIM\_Processor

| Operation              | Requirement | Messages |

|------------------------|-------------|----------|

| GetInstance            | Mandatory   | None     |

| Associators            | Mandatory   | None     |

| AssociatorNames        | Mandatory   | None     |

| References             | Mandatory   | None     |

| ReferenceNames         | Mandatory   | None     |

| EnumerateInstances     | Mandatory   | None     |

| EnumerateInstanceNames | Mandatory   | None     |

#### 434 **8.5 CIM\_ConcreteDependency**

435 Conformant implementations of this profile shall support the operations listed in Table 6 for the

436 CIM\_ConcreteDependency class. Each operation shall be supported as defined in <u>DSP0200</u>.

437

#### Table 6 – Operations: CIM\_ConcreteDependency

| Operation              | Requirement | Messages |

|------------------------|-------------|----------|

| GetInstance            | Mandatory   | None     |

| EnumerateInstances     | Mandatory   | None     |

| EnumerateInstanceNames | Mandatory   | None     |

#### 438 **8.6 CIM\_AssociatedMemory**

439 Conformant implementations of this profile shall support the operations listed in Table 7 for the

440 CIM\_AssociatedMemory class. Each operation shall be supported as defined in <u>DSP0200</u>.

| Table 7 – Operations: CIM_/ | AssociatedMemory |

|-----------------------------|------------------|

|-----------------------------|------------------|

| Operation              | Requirement | Messages |

|------------------------|-------------|----------|

| GetInstance            | Mandatory   | None     |

| EnumerateInstances     | Mandatory   | None     |

| EnumerateInstanceNames | Mandatory   | None     |

#### 442 **8.7 CIM\_BasedOn**

- 443 Conformant implementations of this profile shall support the operations listed in Table 8 for the

- 444 CIM\_BasedOn class. Each operation shall be supported as defined in <u>DSP0200</u>.

#### Table 8 – Operations: CIM\_BasedOn

| Operation              | Requirement | Messages |

|------------------------|-------------|----------|

| GetInstance            | Mandatory   | None     |

| EnumerateInstances     | Mandatory   | None     |

| EnumerateInstanceNames | Mandatory   | None     |

#### 446 9 Use cases

447 This clause contains object diagrams and use cases for the *Multi-type System Memory Profile*.

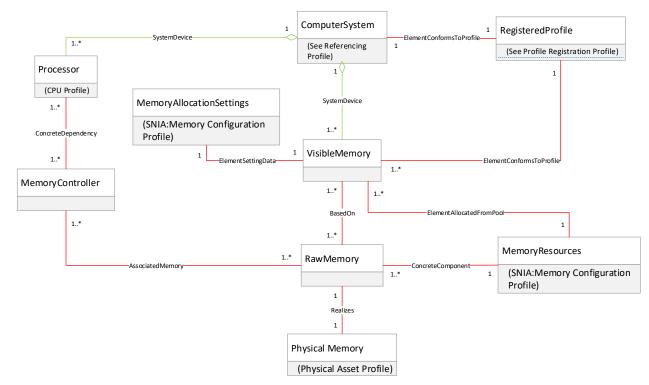

#### 448 9.1 Advertising profile conformance

- 449 Figure 2 shows how an instance of CIM\_RegisteredProfile is used to indicate the presence of a

- 450 conforming implementation of the *Multi-type System Memory Profile* and to identify instances of its central 451 class CIM\_VisibleMemory.

452

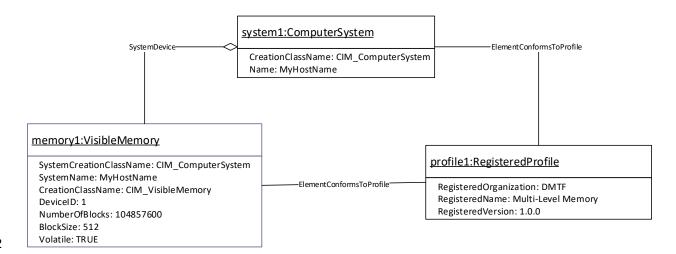

#### 9.2 Single visible memory extent 454

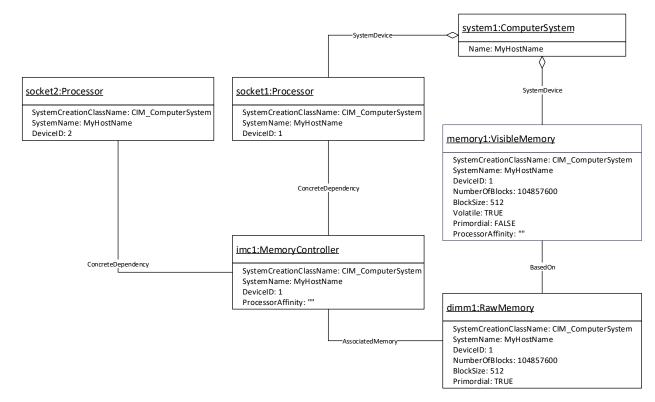

Figure 3 shows the simplest possible configuration with a single memory module (dimm1) contributing its 455 full capacity to a single memory extent (memory1). 456

457

Figure 3 – Single visible memory extent object diagram

#### 9.3 Two visible memory extents 459

460 Figure 4 models a system configuration in which memory modules and the memory controller support configuring memory address ranges with unique quality of service characteristics. In this example a single 461 462 memory module has been configured so as to expose two CIM VisibleMemory extents to the system. Figure 4 shows 1 extent as volatile and the other persistent; the quality of service between the two 463 extents is sufficiently different that one would likely manage and use the extents separately. 464

Exposing the relationship between CIM RawMemory and CIM VisibleMemory extents allows clients to 465 understand reliability and serviceability characteristics of each extent. Clients utilize the CIM BasedOn 466 association to determine the memory module(s) which host any given CIM VisibleMemory instance. The 467 468 position of any given memory module within the system is determined by following the

469 CIM AssociatedMemory association to the CIM MemoryController instance.

470

#### Figure 4 – Distinct visible memory extents object diagram

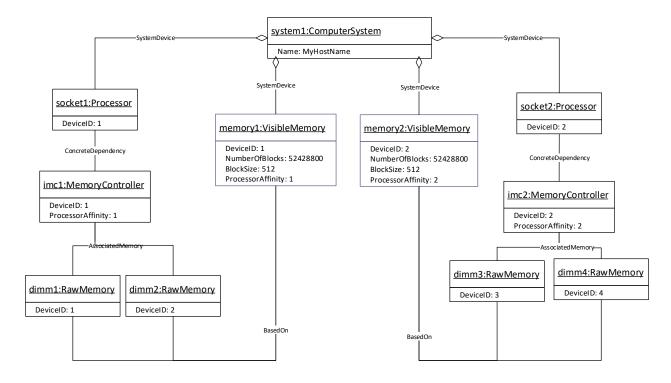

#### 472 9.4 Uniform memory access extents

473 Figure 5 shows a system with a two-processor UMA architecture. The ProcessorAffinity attribute of the

474 CIM\_VisibleMemory instance is set to an empty string indicating no specific affinity. The

475 CIM\_RawMemory instance is associated to a CIM\_MemoryController which services memory accesses

476 from both CIM\_Processor instances. The CIM\_MemoryController.ProcessorAffinity attribute is also set to

the empty string indicating no affinity to a specific processor.

479

Figure 5 – UMA configuration object diagram

#### 480 **9.5** Non-Uniform Memory Access (NUMA) extents

Figure 6 shows the model for a multi-processor system with memory extents organized to support NUMA. The CIM\_VisibleMemory.ProcessorAffinity property is set to indicate affinity consistent with the results that can be achieved via association traversal (i.e., set to the DeviceID of the affiliated processor). The

484 CIM\_MemoryController.ProcessorAffinity is likewise set to the DeviceID of the processor it supports.

In a single processor system (essentially the left or right half of diagram 9-5 in isolation) processor affinity

is set to the identity of the only processor.

488

Figure 6 – NUMA configuration object diagram

#### 489 **9.6 Determine persistent memory capacity**

Determining the capacity of memory with a given QoS is determined by enumerating the

CIM\_VisibleMemory instances with that QoS and examining the NumberOfBlocks and BlockSize

attributes. In Figure 4 above there are two equally sized instances, one offers volatile memory, the other

persistent. Enumerating VisibleMemory instances and summing capacity for those with the Volatile

property set to FALSE would give the total memory capacity offering a persistent QoS. Similarly summing

the capacity of VisibleMemory instances whose Volatile property is set to TRUE would give the total

memory capacity offering a volatile QoS.

#### 497 **9.7** Determine total installed memory capacity

Total installed memory (in bytes) is calculated by enumerating RawMemory instances and summing the product of NumberOfBlocks and BlockSize.

#### 500 9.8 Determine capacity by processor affinity

Capacity available to a given processor is determined by following the CIM\_ConcreteDependency

association to find CIM\_MemoryController instances and then following the AssociatedMemory

association to CIM\_RawMemory instances. Summing the NumberOfBlocks property for the

CIM\_RawMemory instances, so located, determines the total capacity with an affinity to the selected

processor. In Figure 6, the total capacity with an affinity to the processor in socket 2 is determined by

summing the capacity of dimm3 and dimm4.

#### 507 **9.9 Determine processor affinity for visible memory**

508 Determining whether a given CIM\_VisibleMemory instance (assuming the system has a NUMA 509 architecture as given in Figure 6) has NUMA performance characteristics is determined by following the 510 CIM\_BasedOn association to the CIM\_RawMemory instances. From there, the CIM\_AssociatedMemory 511 association is used to verify that each instance of CIM\_RawMemory is controlled by a single processor. 512 Alternatively, the ProcessorAffinity property maybe sufficient to determine affinity for implementations that 513 utilize it.

#### 514 **10 CIM Elements**

Table 9 shows the instances of CIM Elements for this profile. Instances of the following CIM Elements

516 shall be implemented as described in Table 9. Clauses 7 ("Implementation") and 8 ("Methods") may

517 impose additional requirements on these elements.

518

#### Table 9 – CIM Elements – Multi-type System Memory Profile

| Element Name           | Requirement | Description               |

|------------------------|-------------|---------------------------|

| CIM_RegisteredProfile  | Mandatory   | See subclause 10.1        |

| CIM_VisibleMemory      | Mandatory   | See subclause 10.2, 7.2   |

| CIM_RawMemory          | Mandatory   | See subclause 10.3, 7.1   |

| CIM_MemoryController   | Optional    | See subclause 10.4, 7.3.1 |

| CIM_Processor          | Optional    | See subclause 10.5, 7.3.2 |

| CIM_ConcreteDependency | Mandatory   | See subclause 10.6        |

| CIM_SystemDevice       | Mandatory   | See subclause 10.7        |

| CIM_AssociatedMemory   | Mandatory   | See subclause 10.8        |

| CIM_BasedOn            | Mandatory   | See subclause 10.9        |

#### 519 **10.1 CIM\_RegisteredProfile**

CIM\_RegisteredProfile identifies the *Multi-type System Memory Profile* in order for a client to determine

whether an instance of CIM\_VisibleMemory is conformant with this profile. The CIM\_RegisteredProfile

class is defined by the *Profile Registration Profile*. With the exception of the mandatory values specified

for the properties below, the behavior of the CIM\_RegisteredProfile instance is per the *Profile Registration Profile*. Table 10 contains the requirements for elements of this class.

525

#### Table 10 – Class: CIM\_RegisteredProfile

| Elements               | Requirement | Notes                                                           |

|------------------------|-------------|-----------------------------------------------------------------|

| RegisteredName         | Mandatory   | This property shall have a value of "Multi-type System Memory". |

| RegisteredVersion      | Mandatory   | This property shall have a value of "1.0.0".                    |

| RegisteredOrganization | Mandatory   | This property shall have a value of 2 (DMTF).                   |

#### 526 **10.2 CIM\_VisibleMemory**

527 The CIM\_VisibleMemory class represents memory configured with a given set of QoS attributes.

528 Conformant implementations support attributes as given below.

529

#### Table 11 – Class: CIM\_VisibleMemory

| Elements                | Requirement | Notes                                                                 |

|-------------------------|-------------|-----------------------------------------------------------------------|

| CreationClassName       | Mandatory   | Кеу                                                                   |

| DeviceID                | Mandatory   | Кеу                                                                   |

| SystemCreationClassName | Mandatory   | Кеу                                                                   |

| SystemName              | Mandatory   | Кеу                                                                   |

| Primordial              | Mandatory   | False                                                                 |

| BlockSize               | Mandatory   | Number of bytes per block. See subclause 7.2.3                        |

| NumberOfBlocks          | Mandatory   | Block count; multiply by BlockSize to get bytes. See subclause 7.2.3. |

| OperationalStatus       | Mandatory   | None                                                                  |

| HealthState             | Mandatory   | See subclause 7.2.1                                                   |

| EnabledState            | Mandatory   | See subclause 7.2.2                                                   |

| Volatile                | Optional    | None                                                                  |

| AccessGranularity       | Optional    | Access type. See subclause 7.2.4                                      |

| ProcessorAffinity       | Optional    | Affiliated processor. See subclause 7.3.3                             |

| Replication             | Optional    | Data replication. See subclause 7.2.5                                 |

#### 530 **10.3 CIM\_RawMemory**

531 The CIM\_RawMemory class represents of the capacity of a given physical memory module. Conformant 532 implementations support attributes as given below.

533

#### Table 12 – Class: CIM\_RawMemory

| Elements                | Requirement | Notes                                            |

|-------------------------|-------------|--------------------------------------------------|

| CreationClassName       | Mandatory   | Кеу                                              |

| DeviceID                | Mandatory   | Кеу                                              |

| SystemCreationClassName | Mandatory   | Кеу                                              |

| SystemName              | Mandatory   | Кеу                                              |

| Primordial              | Mandatory   | True                                             |

| BlockSize               | Mandatory   | Number of bytes per block                        |

| NumberOfBlocks          | Mandatory   | Block count; multiply by BlockSize to get bytes. |

| OperationalStatus       | Mandatory   | None                                             |

| HealthState             | Mandatory   | None                                             |

#### 534 **10.4 CIM\_MemoryController**

535 The CIM\_MemoryController class represents the controller for one or more raw memory regions. Memory

controller modeling is included in this profile to provide an understanding of the system memory topology.

Conformant implementations support attributes as given below.

Table 13 – Class: CIM\_MemoryController

| Elements                | Requirement | Notes                                    |

|-------------------------|-------------|------------------------------------------|

| CreationClassName       | Mandatory   | Кеу                                      |

| DeviceID                | Mandatory   | Кеу                                      |

| SystemCreationClassName | Mandatory   | Кеу                                      |

| SystemName              | Mandatory   | Кеу                                      |

| ProtocolSupported       | Optional    | Identify controller protocol, e.g., DDR3 |

| ProcessorAffinity       | Optional    | Processor affinity. See subclause 7.3.3  |

#### 539 **10.5 CIM\_Processor**

540 The CIM\_Processor class models a processor with access to a visible memory region. This usage of

541 CIM\_Processor includes only those properties useful in identifying a processor instance. When

542 implementing both Multi-type System Memory and the CPU Profiles, Multi-type System Memory profile

543 can refer to instances created in accordance with the CPU Profile. When only the Multi-type System

544 Memory profile is implemented the more limited version given below is used. This class is mandatory to

545 remove any ambiguity as to the NUMA/UMA nature of the memory architecture. Conformant

546 implementations support attributes as given below.

547

#### Table 14 – Class: CIM\_Processor

| Elements                | Requirement | Notes                                                                                                                                                                                                       |

|-------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CreationClassName       | Mandatory   | Кеу                                                                                                                                                                                                         |

| DeviceID                | Mandatory   | Кеу                                                                                                                                                                                                         |

| SystemCreationClassName | Mandatory   | Кеу                                                                                                                                                                                                         |

| SystemName              | Mandatory   | Кеу                                                                                                                                                                                                         |

| Family                  | Optional    | This property supported if it can be used to determine processor support for specific memory management features.                                                                                           |

| OtherFamilyDescription  | Conditional | Used if Family value is "1".                                                                                                                                                                                |

| Stepping                | Optional    | This property supported if it can be used to determine processor support for specific memory management features.                                                                                           |

| OtherIdentifyingInfo    | Optional    | This property supported if it can be used to determine<br>processor support for specific memory management<br>features. Recommended values: Processor Type,<br>Processor Model, and Processor Manufacturer. |

| IdentifyingDescriptions | Conditional | If OtherIdentifyingInfo is used.                                                                                                                                                                            |

#### 548 **10.6 CIM\_ConcreteDependency**

549 The CIM\_ConcreteDependency association is used to relate an instance of CIM\_MemoryController to a 550 CIM\_Processor instance. Table 15 contains the requirements for elements of this class. 551

|            |             | - 1 7                                                                                                                            |

|------------|-------------|----------------------------------------------------------------------------------------------------------------------------------|

| Elements   | Requirement | Notes                                                                                                                            |

| Antecedent | Mandatory   | This property shall be a reference to an instance of the CIM_Processor class.<br>Cardinality is "1*".                            |

| Dependency | Mandatory   | This property shall be a reference to an instance of a concrete subclass of the CIM_MemoryController class. Cardinality is "1*". |

#### Table 15 – Class: CIM ConcreteDependency

#### 10.7 CIM\_SystemDevice 552

#### 10.7.1 Relating CIM\_Processor to CIM\_ComputerSystem 553

- CIM\_SystemDevice association is used to relate an instance of CIM\_Processor with an instance of 554

- CIM\_ComputerSystem. Table 16 contains the requirements for elements of this class. 555

556

| Table 16 – Class: CIM_Sy | stemDevice – use 1 |

|--------------------------|--------------------|

|--------------------------|--------------------|

| Elements       | Requirement | Notes                                                                                           |

|----------------|-------------|-------------------------------------------------------------------------------------------------|

| GroupComponent | Mandatory   | This property shall be a reference to an instance of CIM_ComputerSystem.<br>Cardinality is "1". |

| PartComponent  | Mandatory   | This property shall be a reference to an instance of CIM_Processor.                             |

|                |             | Cardinality is "1*".                                                                            |

#### 10.7.2 Relating CIM\_VisibleMemory to CIM\_ComputerSystem 557

CIM\_SystemDevice association is used to relate an instance of CIM\_VisibleMemory with an instance of 558 CIM\_ComputerSystem. Table 16 contains the requirements for elements of this class. 559

560

#### Table 17 – Class: CIM\_SystemDevice – use 2

| Elements       | Requirement | Notes                                                                    |

|----------------|-------------|--------------------------------------------------------------------------|

| GroupComponent | Mandatory   | This property shall be a reference to an instance of CIM_ComputerSystem. |

|                |             | Cardinality is "1".                                                      |

| PartComponent  | Mandatory   | This property shall be a reference to an instance of CIM_VisibleMemory.  |

|                |             | Cardinality is "1*".                                                     |

#### 561 **10.8 CIM\_AssociatedMemory**

562 The CIM\_AssociatedMemory association is used to relate the CIM\_MemoryController instance to the 563 CIM\_RawMemory instance to which it applies. Table 18 contains the requirements for elements of this 564 class.

565

| Table 18 – Class: CIM_As | sociatedMemory |

|--------------------------|----------------|

|--------------------------|----------------|

| Elements   | Requirement | Notes                                                                                |

|------------|-------------|--------------------------------------------------------------------------------------|

| Antecedent | Mandatory   | This property shall be a reference to an instance of the CIM_RawMemory class.        |

|            |             | Cardinality is "1*".                                                                 |

| Dependent  | Mandatory   | This property shall be a reference to an instance of the CIM_MemoryController class. |

|            |             | Cardinality is "1*".                                                                 |

#### 566 **10.9 CIM\_BasedOn**

567 The CIM\_BasedOn association is used to relate the CIM\_VisibleMemory to the CIM\_RawMemory on 568 which it is hosted. Table 19 contains the requirements for elements of this class.

569

#### Table 19 – Class: CIM\_BasedOn

| Elements   | Requirement | Notes                                                                         |

|------------|-------------|-------------------------------------------------------------------------------|

| Antecedent | Mandatory   | This property shall be a reference to an instance of the CIM_RawMemory class. |

|            |             | Cardinality is "1".                                                           |

| Dependent  | Mandatory   | This property shall be a reference to an instance of the CIM_VisibleMemory.   |

|            |             | Cardinality is "1".                                                           |

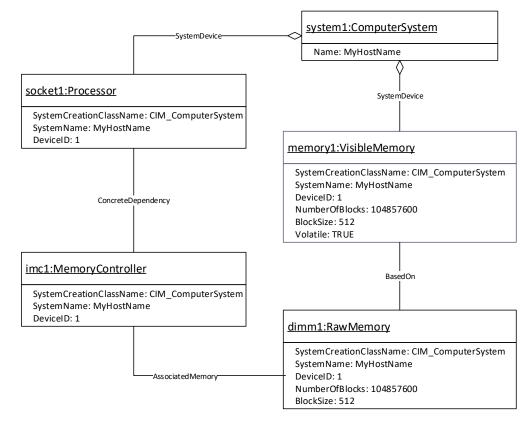

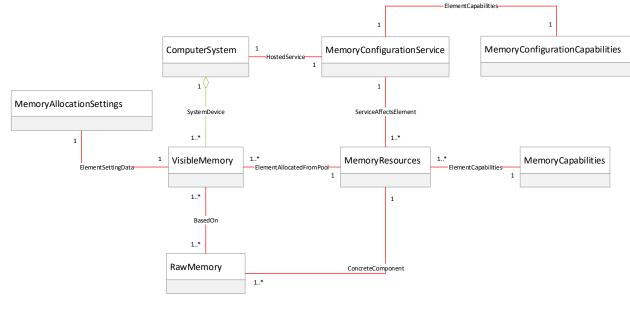

ANNEX A

(informative)

SNIA Memory Configuration Profile

This profile, the Multi-type System Memory Profile is being pursued with the DMTF while a closely related 574 profile tentatively named the Memory Configuration Profile is being pursued with SNIA. Since memory 575 576 management has been the purview of the DMTF it was felt that the static view defined by the Multi-type 577 System Memory Profile was best pursued with the DMTF as a follow-on to the existing System Memory 578 Profile. The management of memory configuration is being pursued with SNIA for similar reasons, its 579 similarity to existing SNIA profiles and the blurring of the typical roles played by memory and storage. 580 Indeed, the primary motivation for updating memory management profiles at this time is the recent 581 introduction of non-volatile memory technologies that use typical memory form factors (e.g., DIMM) and 582 typical memory interconnects (e.g., DDR3) but have features/characteristics usually associated with 583 storage.

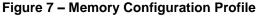

584 The SNIA Memory Configuration Profile is conceived as building upon the Multi-type System Memory 585 Profile. As such its detailed definition is trailing the definition provided in this document. That said, some 586 high-level definition has occurred and may be useful in putting the Multi-type System Memory Profile in 587 context. Figure 7 below identifies key classes in the Memory Configuration Profile focusing on those that

588 associate with Multi-type System Memory Profile classes.

590

- **ComputerSystem** from the referencing profile

- VisibleMemory the central class of the Multi-type System Memory Profile. A system visible memory resource.

- **RawMemory** referenced from the Multi-type System Memory Profile, a primordial memory extent associated with a specific memory module.

| 596<br>597        | • | <b>MemoryAllocationSettings</b> – the settings provided during the provisioning process that resulted in a given VisibleMemory instance. Also used as input to the provisioning extrinsic method.                                           |

|-------------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 598<br>599<br>600 | • | <b>MemoryAllocationService</b> – provides extrinsic methods for memory configuration. These methods result in the allocation or return of resources to the MemoryResources pool and the creation or destruction of VisibleMemory instances. |

| 601<br>602        | • | <b>MemoryConfigurationCapabilities</b> – describes the supported extrinsic method support available from the MemoryAllocationService.                                                                                                       |

| 603<br>604        | • | <b>MemoryCapabilities</b> – describes the configurable features of the resources aggregated under the MemoryResources pool.                                                                                                                 |

# 605ANNEX B606(informative)607608608Change log

| Version | Date       | Description |

|---------|------------|-------------|

| 1.0.0   | 2017-01-19 |             |

|         |            |             |