2

Document Number: DSP1022

3

Date: 2015-05-22

4

Version: 1.0.2

## **5 CPU Profile**

1

- 6 Supersedes: 1.0.1

- 7 Document Class: Normative

- 8 Document Status: Published

- 9 Document Language: en-US

10 Copyright Notice

11 Copyright © 2008–2015 Distributed Management Task Force, Inc. (DMTF). All rights reserved.

DMTF is a not-for-profit association of industry members dedicated to promoting enterprise and systems management and interoperability. Members and non-members may reproduce DMTF specifications and documents, provided that correct attribution is given. As DMTF specifications may be revised from time to time, the particular version and release date should always be noted.

16 Implementation of certain elements of this standard or proposed standard may be subject to third party

17 patent rights, including provisional patent rights (herein "patent rights"). DMTF makes no representations

18 to users of the standard as to the existence of such rights, and is not responsible to recognize, disclose, 19 or identify any or all such third party patent right, owners or claimants, nor for any incomplete or

inaccurate identification or disclosure of such rights, owners or claimants. DMTF shall have no liability to

any party, in any manner or circumstance, under any legal theory whatsoever, for failure to recognize,

disclose, or identify any such third party patent rights, or for such party's reliance on the standard or

23 incorporation thereof in its product, protocols or testing procedures. DMTF shall have no liability to any

24 party implementing such standard, whether such implementation is foreseeable or not, nor to any patent

25 owner or claimant, and shall have no liability or responsibility for costs or losses incurred if a standard is

26 withdrawn or modified after publication, and shall be indemnified and held harmless by any party

implementing the standard from any and all claims of infringement by a patent owner for such

28 implementations.

29 For information about patents held by third-parties which have notified the DMTF that, in their opinion,

30 such patent may relate to or impact implementations of DMTF standards, visit

31 <u>http://www.dmtf.org/about/policies/disclosures.php</u>.

32 This document's normative language is English. Translation into other languages is permitted.

## CONTENTS

| 34 | Foreword |                               |                                                                            |      |

|----|----------|-------------------------------|----------------------------------------------------------------------------|------|

| 35 | Intro    | oductio                       | n                                                                          | 7    |

| 36 | 1        | Scope                         |                                                                            |      |

| 37 | 2        | Normative references          |                                                                            |      |

| 38 | 3        | Terms and definitions         |                                                                            |      |

| 39 |          | Symbols and abbreviated terms |                                                                            |      |

|    | 4        | ,                             |                                                                            |      |

| 40 | 5        |                               | osis                                                                       |      |

| 41 | 6        |                               | iption                                                                     |      |

| 42 | 7        |                               | mentation                                                                  |      |

| 43 |          | 7.1                           | CIM_Processor                                                              |      |

| 44 |          | 7.2                           | Processor capabilities                                                     |      |

| 45 |          | 7.3                           | Processor state management                                                 |      |

| 46 |          | 7.4                           | CIM_Processor.RequestedState                                               |      |

| 47 |          | 7.5                           | Modeling the current enabled state of the processor                        |      |

| 48 |          | 7.6                           | Modeling individual processor cores                                        |      |

| 49 |          | 7.7                           | Modeling individual hardware threads                                       |      |

| 50 |          | 7.8                           | Modeling cache memory                                                      |      |

| 51 |          | 7.9                           | Modeling physical aspects of processor and cache memory                    |      |

| 52 | 8        | Metho                         | ods                                                                        | . 22 |

| 53 |          | 8.1                           | CIM_Processor.RequestStateChange()                                         | . 22 |

| 54 |          | 8.2                           | CIM_ProcessorCore.RequestStateChange()                                     |      |

| 55 |          | 8.3                           | CIM_HardwareThread.RequestStateChange()                                    | . 24 |

| 56 |          | 8.4                           | CIM_Memory.RequestStateChange()                                            | . 25 |

| 57 |          | 8.5                           | Profile conventions for operations                                         |      |

| 58 |          | 8.6                           | CIM_AssociatedCacheMemory                                                  |      |

| 59 |          | 8.7                           | CIM_ConcreteComponent — References CIM_HardwareThread and CIM_Processor    |      |

| 60 |          | 8.8                           | CIM_ConcreteComponent — References CIM_ProcessorCore and CIM_Processor     | . 26 |

| 61 |          | 8.9                           | CIM_ElementCapabilities — References CIM_HardwareThread and                |      |

| 62 |          |                               | CIM_EnabledLogicalElementCapabilities                                      | . 27 |

| 63 |          | 8.10                          | CIM_ElementCapabilities — References CIM_Memory and                        |      |

| 64 |          |                               | CIM_EnabledLogicalElementCapabilities                                      | . 27 |

| 65 |          | 8.11                          | CIM_ElementCapabilities — References CIM_Processor and                     |      |

| 66 |          |                               | CIM_ProcessorCapabilities                                                  | . 27 |

| 67 |          | 8.12                          | CIM_ElementCapabilities — References CIM_ProcessorCore and                 |      |

| 68 |          |                               | CIM_EnabledLogicalElementCapabilities                                      |      |

| 69 |          | 8.13                          | CIM_EnabledLogicalElementCapabilities                                      | . 28 |

| 70 |          | 8.14                          | CIM_HardwareThread                                                         |      |

| 71 |          | 8.15                          | CIM_Memory                                                                 | . 29 |

| 72 |          | 8.16                          | CIM_Processor                                                              |      |

| 73 |          | 8.17                          | CIM_ProcessorCapabilities                                                  | . 29 |

| 74 |          | 8.18                          | CIM_ProcessorCore                                                          | . 30 |

| 75 |          | 8.19                          | CIM_SystemDevice                                                           | . 30 |

| 76 | 9        | Use c                         | ases                                                                       | . 31 |

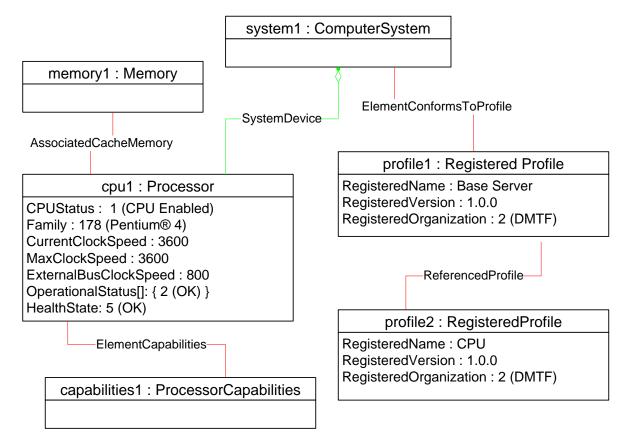

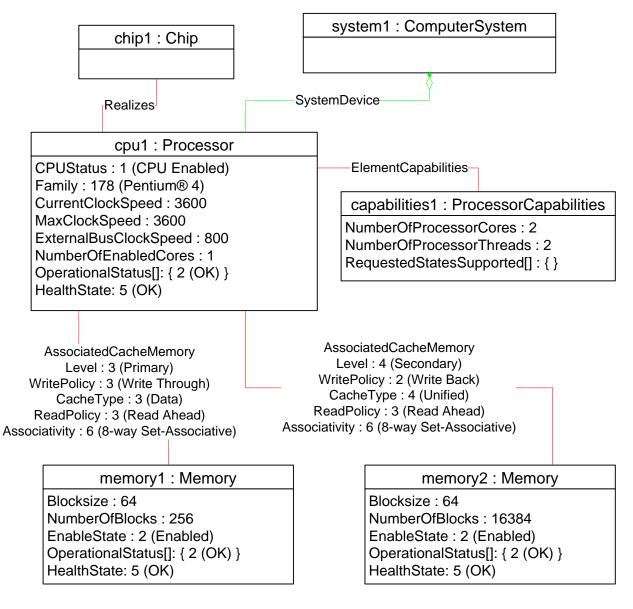

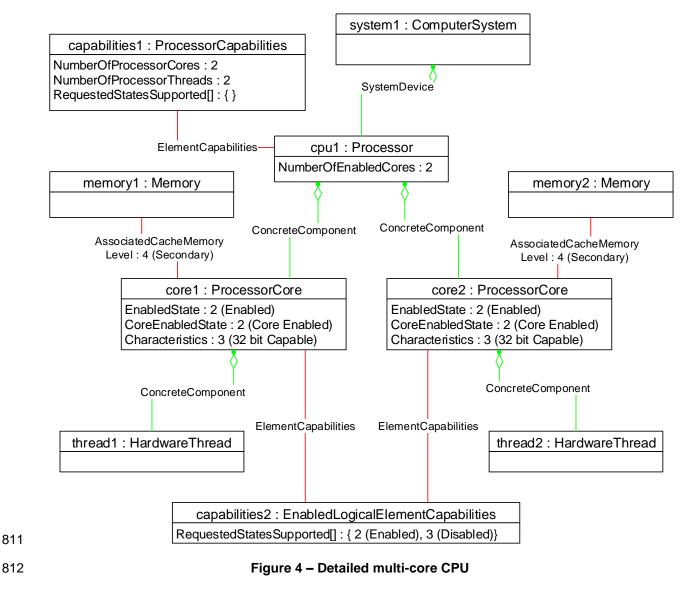

| 77 |          | 9.1                           | Object diagrams                                                            | . 31 |

| 78 |          | 9.2                           | Change the enabled state of the memory to the desired state                |      |

| 79 |          | 9.3                           | Change the enabled state of the CPU to the desired state                   |      |

| 80 |          | 9.4                           | Change the enabled state of the CPU's core to the desired state            |      |

| 81 |          | 9.5                           | Change the enabled state of the CPU's hardware thread to the desired state |      |

| 82 |          | 9.6                           | Retrieve all the processor cores for the CPU                               |      |

| 83 |          | 9.7                           | Retrieve all the hardware threads for the CPU                              | . 38 |

| 84 |          | 9.8                           | Retrieve CPU's cache memory information for the CPU                        | . 38 |

| 85  | 10  | CIM Elements                                                                | 38 |

|-----|-----|-----------------------------------------------------------------------------|----|

| 86  |     | 10.1 CIM_AssociatedCacheMemory                                              | 40 |

| 87  |     | 10.2 CIM_ConcreteComponent — References CIM_HardwareThread and              |    |

| 88  |     | CIM_ProcessorCore                                                           | 40 |

| 89  |     | 10.3 CIM_ConcreteComponent — References CIM_ProcessorCore and CIM_Processor | 41 |

| 90  |     | 10.4 CIM_ElementCapabilities — References CIM_HardwareThread and            |    |

| 91  |     | CIM_EnabledLogicalElementCapabilities                                       | 41 |

| 92  |     | 10.5 CIM_ElementCapabilities — References CIM_Memory and                    |    |

| 93  |     | CIM_EnabledLogicalElementCapabilities                                       | 41 |

| 94  |     | 10.6 CIM_ElementCapabilities — References CIM_Processor and                 |    |

| 95  |     | CIM_ProcessorCapabilities                                                   | 42 |

| 96  |     | 10.7 CIM_ElementCapabilities — References CIM_ProcessorCore and             |    |

| 97  |     | CIM_EnabledLogicalElementCapabilities                                       | 42 |

| 98  |     | 10.8 CIM_EnabledLogicalElementCapabilities                                  | 43 |

| 99  |     | 10.9 CIM_HardwareThread                                                     | 43 |

| 100 |     | 10.10 CIM_Memory                                                            |    |

| 101 |     | 10.11 CIM_Processor                                                         | 44 |

| 102 |     | 10.12 CIM_ProcessorCapabilities                                             | 44 |

| 103 |     | 10.13 CIM_ProcessorCore                                                     | 45 |

| 104 |     | 10.14 CIM_RegisteredProfile                                                 | 45 |

| 105 |     | 10.15 CIM_SystemDevice                                                      | 45 |

| 106 | ANN | NEX A (informative) Change log                                              | 47 |

| 107 |     |                                                                             |    |

## 108 Figures

| 109 | Figure 1 – CPU Profile: Class Diagram             | 12 |

|-----|---------------------------------------------------|----|

| 110 | Figure 2 – Registered Profile                     | 31 |

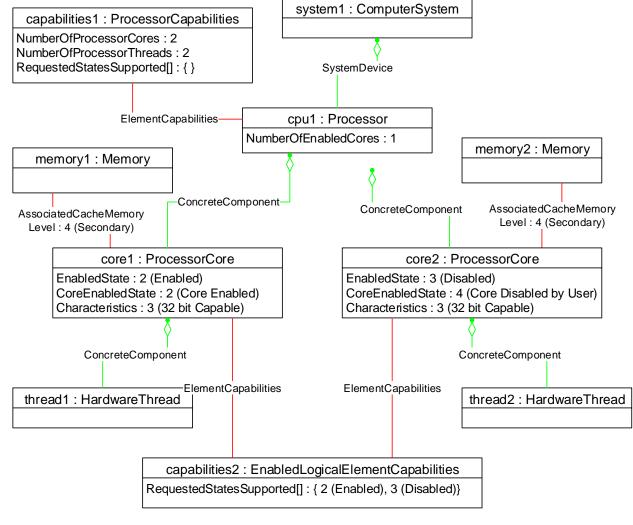

| 111 | Figure 3 – Multi-core CPU                         | 32 |

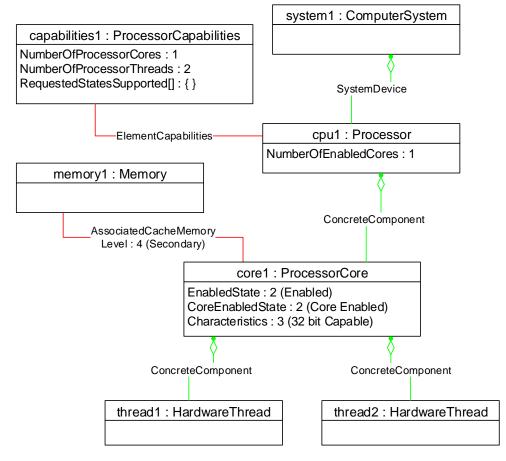

| 112 | Figure 4 – Detailed multi-core CPU                | 33 |

| 113 | Figure 5 – Multi-core CPU with a disabled core    | 34 |

| 114 | Figure 6 – Single Core, Multi-Hardware Thread CPU | 35 |

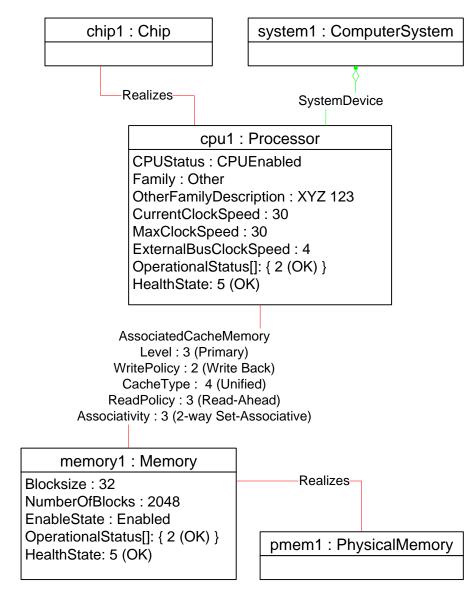

| 115 | Figure 7 – Processor with Off-Chip Cache          | 36 |

| 116 |                                                   |    |

## 117 **Tables**

| 118 | Table 1 – Related Profiles                                                           | 10 |

|-----|--------------------------------------------------------------------------------------|----|

| 119 | Table 2 – CIM_ProcessorCapabilities Properties mapping to SMBIOS equivalence         | 13 |

| 120 | Table 3 – CIM_Processor.CPUStatus Value Descriptions                                 | 15 |

| 121 | Table 4 – Mapping for CPUStatus Property and EnabledState Property Values            | 15 |

| 122 | Table 5 – CIM_ProcessorCore.CoreEnabledState Value Descriptions                      | 17 |

| 123 | Table 6 – Mapping for the CoreEnabledState property and EnabledState property values | 18 |

| 124 | Table 7 – CIM_HardwareThread.EnabledState Value Descriptions                         | 20 |

| 125 | Table 8 – CIM_Memory.EnabledState value descriptions                                 | 22 |

| 126 | Table 9 – CIM_Processor.RequestStateChange() method: Return code values              | 23 |

| 127 | Table 10 – CIM_Processor.RequestStateChange() method: Parameters                     | 23 |

| 128 | Table 11 – CIM_ProcessorCore.RequestStateChange() method: Return code values         | 23 |

| 129 | Table 12 – CIM_ProcessorCore.RequestStateChange() method: Parameters                 | 24 |

| 130 | Table 13 – CIM_HardwareThread.RequestStateChange() method: Return code values        | 24 |

| 131        | Table 14 – CIM_HardwareThread.RequestStateChange() method: Parameters                                                                                                       | . 24 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 132        | Table 15 – CIM_Memory.RequestStateChange() method: Return code values                                                                                                       | . 25 |

| 133        | Table 16 – CIM_Memory.RequestStateChange() method: Parameters                                                                                                               | . 25 |

| 134        | Table 17 – Operations: CIM_AssociatedCacheMemory                                                                                                                            | . 26 |

| 135        | Table 18 – Operations: CIM_ConcreteComponent                                                                                                                                | . 26 |

| 136        | Table 19 – Operations: CIM_ConcreteComponent                                                                                                                                |      |

| 137        | Table 20 – Operations: CIM_ElementCapabilities                                                                                                                              |      |

| 138        | Table 21 – Operations: CIM_ElementCapabilities                                                                                                                              |      |

| 139        | Table 22 – Operations: CIM_ElementCapabilities                                                                                                                              | . 28 |

| 140        | Table 23 – Operations: CIM_ElementCapabilities                                                                                                                              |      |

| 141        | Table 24 – Operations: CIM_HardwareThread                                                                                                                                   |      |

| 142        | Table 25 – Operations: CIM_Memory                                                                                                                                           |      |

| 143        | Table 26 – Operations: CIM_Processor                                                                                                                                        |      |

| 144        | Table 27 – Operations: CIM_ProcessorCore                                                                                                                                    |      |

| 145        | Table 28 – Operations: CIM_SystemDevice                                                                                                                                     |      |

| 146        | Table 29 – CIM Elements: CPU Profile                                                                                                                                        |      |

| 147        | Table 30 – Class: CIM_AssociatedCacheMemory                                                                                                                                 | . 40 |

| 148        | Table 31 – Class: CIM_ConcreteComponent — References CIM_HardwareThread and                                                                                                 | 40   |

| 149        | CIM_ProcessorCore                                                                                                                                                           |      |

| 150        | Table 32 – Class: CIM_ConcreteComponent — References CIM_ProcessorCore and CIM_Processor .<br>Table 33 – Class: CIM_ElementCapabilities — References CIM_HardwareThread and | .41  |

| 151<br>152 | CIM_EnabledLogicalElementCapabilities                                                                                                                                       | 41   |

| 153        | Table 34 – Class: CIM_ElementCapabilities — References CIM_Memory and                                                                                                       |      |

| 154        | CIM_EnabledLogicalElementCapabilities                                                                                                                                       | . 42 |

| 155        | Table 35 – Class: CIM_ElementCapabilities – References CIM_Processor and                                                                                                    |      |

| 156        | CIM_ProcessorCapabilities                                                                                                                                                   | . 42 |

| 157        | Table 36 – Class: CIM_ElementCapabilities — References CIM_ProcessorCore and                                                                                                |      |

| 158        | CIM_EnabledLogicalElementCapabilities                                                                                                                                       |      |

| 159        | Table 37 – Class: CIM_EnabledLogicalElementCapabilities                                                                                                                     |      |

| 160        | Table 38 – Class: CIM_HardwareThread                                                                                                                                        |      |

| 161        | Table 39 – Class: CIM_Memory                                                                                                                                                |      |

| 162        | Table 40 – Class: CIM_Processor                                                                                                                                             |      |

| 163        | Table 41 – Class: CIM_ProcessorCapabilities                                                                                                                                 |      |

| 164        | Table 42 – Class: CIM_ProcessorCore                                                                                                                                         |      |

| 165        | Table 43 – Class: CIM_RegisteredProfile                                                                                                                                     |      |

| 166        | Table 44 – Class: CIM_SystemDevice                                                                                                                                          | . 46 |

| 168        | Foreword                                                                                                                                                                                                                            |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 169        | The CPU Profile (DSP1022) was prepared by the Physical Platform Profiles Working Group of the DMTF.                                                                                                                                 |

| 170<br>171 | DMTF is a not-for-profit association of industry members dedicated to promoting enterprise and systems management and interoperability. For information about the DMTF, see <a href="http://www.dmtf.org">http://www.dmtf.org</a> . |

| 172        | Acknowledgments                                                                                                                                                                                                                     |

| 173        | The DMTF acknowledges the following individuals for their contributions to this document:                                                                                                                                           |

| 174        | Editors:                                                                                                                                                                                                                            |

| 175        | • Jon Hass – Dell                                                                                                                                                                                                                   |

| 176        | Jeff Hilland – Hewlett-Packard Company                                                                                                                                                                                              |

| 177        | John Leung - Intel                                                                                                                                                                                                                  |

| 178        | Khachatur Papanyan – Dell                                                                                                                                                                                                           |

| 179        | Contributors:                                                                                                                                                                                                                       |

| 180        | • Jeff Lynch – IBM                                                                                                                                                                                                                  |

| 181        | Aaron Merkin – IBM                                                                                                                                                                                                                  |

| 182        | Christina Shaw – Hewlett-Packard Company                                                                                                                                                                                            |

| 183        | Perry Vincent – Intel                                                                                                                                                                                                               |

## Introduction

185 The information in this specification should be sufficient for a provider or consumer of this data to identify

186 unambiguously the classes, properties, methods, and values that shall be instantiated and manipulated to

187 represent and manage the processor components of systems and subsystems modeled using the DMTF

188 Common Information Model (CIM) core and extended model definitions.

189 The target audience for this specification is implementers who are writing CIM-based providers or

190 consumers of management interfaces that represent the component described in this document.

## **CPU Profile**

## 193 **1 Scope**

194 The *CPU Profile* extends the management capability of referencing profiles by adding the capability to 195 represent CPUs or processors in a managed system. CPU cache memory and associations with CPU

196 physical aspects, as well as profile implementation version information, are modeled in this profile.

## 197 **2 Normative references**

198 The following referenced documents are indispensable for the application of this document. For dated or 199 versioned references, only the edition cited (including any corrigenda or DMTF update versions) applies.

- For references without a date or version, the latest published edition of the referenced document

- 201 (including any corrigenda or DMTF update versions) applies.

- 202 DMTF DSP0004, CIM Infrastructure Specification 2.5,

- 203 http://www.dmtf.org/standards/published\_documents/DSP0004\_2.5.pdf

- 204 DMTF DSP0134, System Management BIOS (SMBIOS) Reference Specification 2.6, 205 http://www.dmtf.org/standards/published\_documents/DSP0134\_2.6.pdf

- 206 DMTF DSP0200, CIM Operations over HTTP 1.3,

207 <u>http://www.dmtf.org/standards/published\_documents/DSP0200\_1.3.pdf</u>

- 208 DMTF DSP1001, Management Profile Specification Usage Guide 1.0,

- 209 http://www.dmtf.org/standards/published\_documents/DSP1001\_1.0.pdf

- 210 DMTF DSP1011, Physical Asset Profile 1.0,

- 211 <u>http://www.dmtf.org/standards/published\_documents/DSP1011\_1.0.pdf</u>

- 212 DMTF DSP1033, Profile Registration Profile 1.0,

- 213 <u>http://www.dmtf.org/standards/published\_documents/DSP1033\_1.0.pdf</u>

- 214 IETF RFC5234, Augmented BNF for Syntax Specifications: ABNF, January 2008,

- 215 http://www.rfc-editor.org/rfc/rfc5234.txt

- 216 ISO/IEC Directives, Part 2, <u>Rules for the structure and drafting of International Standards</u>

## 217 **3 Terms and definitions**

In this document, some terms have a specific meaning beyond the normal English meaning. Those termsare defined in this clause.

The terms "shall" ("required"), "shall not," "should" ("recommended"), "should not" ("not recommended"),

"may," "need not" ("not required"), "can" and "cannot" in this document are to be interpreted as described

in <u>ISO/IEC Directives, Part 2</u>, Annex H. The terms in parenthesis are alternatives for the preceding term,

for use in exceptional cases when the preceding term cannot be used for linguistic reasons. Note that

<u>ISO/IEC Directives, Part 2</u>, Annex H specifies additional alternatives. Occurrences of such additional

alternatives shall be interpreted in their normal English meaning.

The terms "clause," "subclause," "paragraph," and "annex" in this document are to be interpreted as described in <u>ISO/IEC Directives, Part 2</u>, Clause 5.

#### **CPU Profile**

- 228 The terms "normative" and "informative" in this document are to be interpreted as described in <u>ISO/IEC</u>

- 229 <u>Directives, Part 2</u>, Clause 3. In this document, clauses, subclauses, or annexes labeled "(informative)" do 230 not contain normative content. Notes and examples are always informative elements.

- For the purposes of this document, the following terms and definitions apply. The terms defined in DSP0004, DSP0200, DSP1001, and DSP1033 also apply to this document.

- 233 **3.1**

#### 234 Cache Memory

- 235 indicates the instance of CIM\_Memory that represents the cache memory for the processor

- 236 **3.2**

- 237 Host Processor

- 238 indicates the instance of CIM\_Processor that represents the processor that hosts the processor core

- 239 **3.3**

#### 240 Threading Processor Core

- 241 indicates the instance of CIM\_ProcessorCore that represents the processor core that enables the

- 242 hardware threading

## 243 4 Symbols and abbreviated terms

- 244 **4.1**

- 245 CPU

- 246 central processing unit

## 247 **5 Synopsis**

- 248 Profile Name: CPU

- 249 Version: 1.0.2

- 250 Organization: DMTF

- 251 CIM Schema Version: 2.19

- 252 Central Class: CIM\_Processor

- 253 Scoping Class: CIM\_ComputerSystem

- 254 The CPU Profile is a component profile that extends the management capability of referencing profiles by

- adding the capability to represent CPUs or processors in a managed system.

- 256

#### Table 1 – Related Profiles

| Profile Name         | Organization | Version | Requirement | Description |

|----------------------|--------------|---------|-------------|-------------|

| Physical Asset       | DMTF         | 1.0     | Optional    | See 7.9.    |

| Profile Registration | DMTF         | 1.0     | Mandatory   |             |

## 257 6 **Description**

The *CPU Profile* describes CPU or processor devices and associated cache memory used in managed systems.

- 260 The profile could manage the following capabilities of a typical computer system:

- A computer system can have one or more processors, which may be individually enabled or disabled.

- A processor can contain one or more processor cores, which may be individually enabled or disabled.

- A processor core can contain one or more hardware threads, which may be individually enabled or disabled

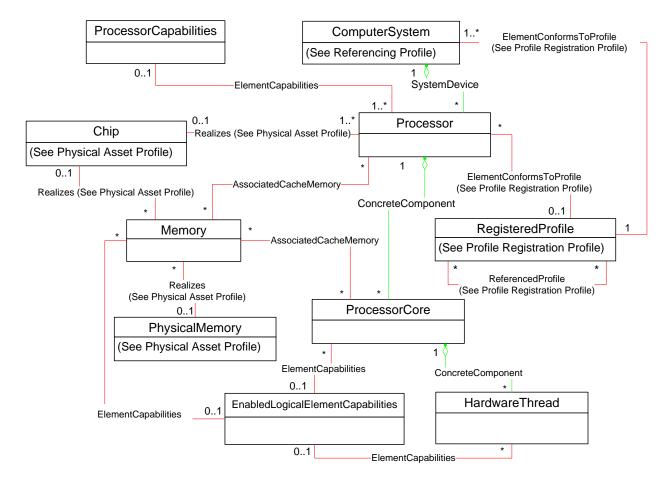

- Figure 1 represents the class schema for the *CPU Profile*. For simplicity, the prefix CIM\_ has been removed from the names of the classes.

- The CIM\_Processor class represents a group of processor cores; the CIM\_ProcessorCapabilities class describes the capabilities of the processor. The CIM\_Processor may be associated to one or more of

- instances of CIM ProcessorCore, through the CIM ConcreteComponent association.

- The CIM\_ProcessorCore class represents a processing execution unit. The CIM\_ProcessorCore may be associated to one or more instances of CIM\_HardwareThread, through the CIM\_ConcreteComponent association.

- The CIM\_HardwareThread class represents a hardware thread, a mechanism by which a processing execute unit is made to appear as multiple processing units (each called a virtual core).

- The CIM\_Memory class represents cache memory. CIM\_Memory may be associated to either CIM\_Processor or CIM\_ProcessorCore, through the CIM\_AssociatedCacheMemory association.

- The CIM\_Chip class represents the physical aspects of a processor. The CIM\_PhysicalMemory represents the cache memory, when the cache memory is off-chip/external.

282

Figure 1 – CPU Profile: Class Diagram

## 283 **7 Implementation**

This clause details the requirements related to the arrangement of instances and their properties for implementations of this profile. Methods are listed in clause 8 ("Methods"), and properties are listed in clause 10 ("CIM Elements").

## 287 **7.1 CIM\_Processor**

288 Zero or more instances of CIM\_Processor shall be instantiated.

## 289 7.2 Processor capabilities

The CIM\_ProcessorCapabilities class may be instantiated to represent the processor capabilities. Only one instance of CIM\_ProcessorCapabilities shall be associated with a given instance of CIM\_Processor through an instance of CIM\_ElementCapabilities.

## 293 **7.2.1 Multi-Core or Multi-Thread processor capabilities**

When modeling the capabilities of a multi-core or multi-thread processor, the CIM\_ProcessorCapabilities class shall be instantiated and associated to the instance of CIM\_Processor that represents the multi-core or multi-thread processor.

- 297 The properties of CIM\_ProcessorCapabilities described in the "CIM\_ProcessorCapabilities Properties"

- column in Table 2 are defined in terms of the <u>DSP0134</u> Processor Information structure to provide meaningful context for the interpretation of the properties. The mappings specified in Table 2 shall be

- 299 meaningful context for the interpretation of the properties. The mappings specified in Table 2 shall

300 used. The underlying represented system does not need to support <u>DSP0134</u>.

301

Table 2 – CIM\_ProcessorCapabilities Properties mapping to SMBIOS equivalence

| CIM_ProcessorCapabilities<br>Properties | SMBIOS Structure<br>Name | SMBIOS Structure Description           |  |

|-----------------------------------------|--------------------------|----------------------------------------|--|

| NumberOfProcessorCores                  | Core Count               | Number of cores per processor socket   |  |

| NumberOfHardwareThreads                 | Thread Count             | Number of threads per processor socket |  |

## 302 **7.2.2** Single-Core and Single-Thread processor capabilities

- 303 When modeling the capabilities of a single-core and single-thread processor, the

- 304 CIM\_ProcessorCapabilities may not be instantiated.

- 305 When no instance of CIM\_ProcessorCapabilities is associated with the instance of CIM\_Processor that 306 represents the processor, the processor is a single-core and single-thread processor.

- 307 When an instance of CIM\_ProcessorCapabilities is associated with the instance of CIM\_Processor that 308 represents the single-core and single-thread processor, the following requirements apply:

- The CIM\_ProcessorCapabilities.NumberOfProcessorCores property shall have a value of 1.

- The CIM\_ProcessorCapabilities.NumberOfHardwareThreads property shall have a value of 1.

### 311 **7.2.3** CIM\_ProcessorCapabilities.RequestedStatesSupported

- 312 The RequestedStatesSupported property is an array that contains the supported requested states for the

- instance of CIM\_Processor. This property shall be the super set of the values to be used as the

- 314 RequestedState parameter in the RequestStateChange() method (see 8.1). The value of the

- 315 CIM\_ProcessorCapabilities.RequestedStatesSupported property shall be an empty array or contain any

- 316 combination of the following values: 2 (Enabled), 3 (Disabled), or 11 (Reset).

### 317 **7.2.4 CIM\_ProcessorCapabilities.ElementNameEditSupported**

The ElementNameEditSupported property shall have a value of TRUE when the implementation supports client modification of the CIM\_Processor.ElementName property.

### 320 **7.2.5** CIM\_ProcessorCapabilities.MaxElementNameLen

The MaxElementNameLen property shall be implemented when the ElementNameEditSupported property has a value of TRUE.

## 323 **7.3 Processor state management**

Processor state management requires that the CIM\_Processor.RequestStateChange() method be

supported (see 8.1) and the value of the CIM\_Processor.RequestedState property not match 12 (Not

Applicable).

### 327 **7.3.1 Processor state management support**

When the instance of CIM\_ProcessorCapabilities does not exist, processor state management shall not be supported. 330 When the value of the CIM\_ProcessorCapabilities.RequestedStatesSupported property of the associated

- CIM\_ProcessorCapabilities instance is an empty array, processor state management shall not be

supported.

- When the value of the CIM\_ProcessorCapabilities.RequestedStatesSupported property of the associated

CIM\_ProcessorCapabilities instance is not an empty array, processor state management shall be

supported.

## 336 **7.4 CIM\_Processor.RequestedState**

- The CIM\_Processor.RequestedState property shall have a value of 12 (Not Applicable) or 5 (No Change),

or a value contained in the CIM\_ProcessorCapabilities.RequestedStatesSupported property array of the

associated CIM\_ProcessorCapabilities instance (see 7.2.2).

- 340 When processor state management is supported and the RequestStateChange() method is successfully 341 executed, the RequestedState property shall be set to the value of the RequestedState parameter of the

- 342 RequestStateChange() method. After the RequestStateChange() method has successfully executed, the

- 343 RequestedState and EnabledState properties shall have equal values with the exception of the

- 344 transitional requested state 11 (Reset). The value of the Requested State property may also change as a

- result of a request for a change to the processor's enabled state by a non-CIM implementation.

## 346 7.4.1 RequestedState — 12 (Not Applicable) value

347 When processor state management is not supported, the value of the CIM\_Processor.RequestedState 348 property shall be 12 (Not Applicable).

## 349 **7.4.2** RequestedState — 5 (No Change) value

350 When processor state management is supported, the initial value of the CIM\_Processor.RequestedState 351 property shall be 5 (No Change).

## 352 **7.5** Modeling the current enabled state of the processor

- 353 The current enabled state of the processor is described by the CIM\_Processor.CPUStatus and

- 354 CIM\_Processor.EnabledState properties. Clauses 7.5.1 and 7.5.2 detail the requirements for

- 355 implementing these two properties.

### 356 7.5.1 CIM\_Processor.CPUStatus

Table 3 describes the mapping between the values of the CIM\_Processor.CPUStatus property and the corresponding description of the state of the processor. The CPUStatus property shall match the values

that are specified in Table 3. When the RequestStateChange() method executes but does not complete

successfully, or the processor is in an indeterminate state, the CPUStatus property shall have value of 0

(Unknown). The value of this property may also change as a result of a change to the processor's

362 enabled state by a non-CIM implementation.

363

| Table 3 – CIM_Processor.CPUStatus Value | Descriptions |

|-----------------------------------------|--------------|

|-----------------------------------------|--------------|

| Value | Description                          | Extended Description                                                                                                                                                                              |

|-------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | Unknown                              | Processor state is indeterminate, or the processor state management is not supported.                                                                                                             |

| 1     | CPU Enabled                          | Processor shall be enabled.                                                                                                                                                                       |

| 2     | CPU Disabled by User                 | Processor shall be disabled through client configuration, which<br>may occur through client invocation of the<br>RequestStateChange() method or through a non-CIM<br>implementation such as BIOS. |

| 3     | CPU Disabled By BIOS (POST<br>Error) | Processor shall be disabled due to a POST error.                                                                                                                                                  |

| 4     | CPU Is Idle, waiting to be enabled   | Processor shall be enabled but idling.                                                                                                                                                            |

#### 364 **7.5.2** CIM\_Processor.EnabledState

365 The CIM\_Processor.EnabledState property shall be implemented in addition to the

366 CIM\_Processor.CPUStatus property. When the CPUStatus property has a value that matches a value in

the "CPUStatus Value" column in Table 4, the EnabledState property shall have a value that matches a

368 value in the "EnabledState Value" column in the same row in the table.

369

#### Table 4 – Mapping for CPUStatus Property and EnabledState Property Values

| CPUStatus Value | Description                          | EnabledState Value | Description                  |

|-----------------|--------------------------------------|--------------------|------------------------------|

| 0               | Unknown                              | 0 or 5             | Unknown or Not<br>Applicable |

| 1               | CPU Enabled                          | 2                  | Enabled                      |

| 2               | CPU Disabled by User                 | 3                  | Disabled                     |

| 3               | CPU Disabled By BIOS (POST<br>Error) | 3                  | Disabled                     |

| 4               | CPU Is Idle, waiting to be enabled   | 2                  | Enabled                      |

## **7.6 Modeling individual processor cores**

371 Modeling the individual processor cores is optional functionality. When individual processor cores are

372 modeled, the implementation shall instantiate an instance of CIM\_ProcessorCore to represent each

- 373 processor core. All the requirements in this clause and its subclauses are applicable when an

- 374 implementation instantiates the CIM\_ProcessorCore class.

- 375 Each instance of CIM\_ProcessorCore shall be associated through an instance of

376 CIM\_ConcreteComponent to only one instance of CIM\_Processor that represents the processor (Host

377 Processor) that hosts the processor core.

- 378 The number of instances of CIM\_ProcessorCore associated with the Host Processor shall be equal to the

- 379 value of the CIM\_ProcessorCapabilities.NumberOfProcessorCores property of the instance of

- 380 CIM\_ProcessorCapabilities that is associated with the Host Processor.

#### 381 **7.6.1 Processor core capabilities**

- The CIM\_EnabledLogicalElementCapabilities class may be used to model the capabilities of processor cores. When the CIM\_EnabledLogicalElementCapabilities class is instantiated to represent the processor core capabilities, the instance of CIM\_EnabledLogicalElementCapabilities shall be associated with the CIM\_ProcessorCore instance through an instance of CIM\_ElementCapabilities and used for advertising the capabilities of the CIM\_ProcessorCore instance.

- There shall be at most one instance of CIM\_EnabledLogicalElementCapabilities associated with a given

instance of CIM\_ProcessorCore.

#### 389 7.6.1.1 CIM\_EnabledLogicalElementCapabilities.RequestedStatesSupported

- 390 The RequestedStatesSupported property is an array that contains the supported requested states for the

- 391 instance of CIM\_ProcessorCore. This property shall be the super set of the values to be used as the

- 392 RequestedState parameter in the RequestStateChange() method (see 8.2). The value of the

- 393 RequestedStatesSupported property shall be an empty array or contain any combination of the following

- 394 values: 2 (Enabled), 3 (Disabled), or 11 (Reset).

#### 395 **7.6.1.2** CIM\_EnabledLogicalElementCapabilities.ElementNameEditSupported

The ElementNameEditSupported property shall have a value of TRUE when the implementation supports client modification of the CIM\_ProcessorCore.ElementName property.

#### 398 **7.6.1.3 CIM\_EnabledLogicalElementCapabilities.MaxElementNameLen**

The MaxElementNameLen property shall be implemented when the ElementNameEditSupported property has a value of TRUE.

#### 401 **7.6.2 Processor core state management**

402 Processor core state management requires that the CIM\_ProcessorCore.RequestStateChange() method

403 be supported (see 8.2) and the value of the CIM\_ProcessorCore.RequestedState property not match 12

404 (Not Applicable).

#### 405 **7.6.2.1 Processor core state management support**

- 406 When no CIM\_EnabledLogicalElementCapabilities instance is associated with the CIM\_ProcessorCore 407 instance, processor core state management shall not be supported.

- 408 When a CIM\_EnabledLogicalElementCapabilities instance is associated with the CIM\_ProcessorCore 409 instance but the value of the CIM\_EnabledLogicalElementCapabilities.RequestedStatesSupported

- 410 property is an empty array, processor core state management shall not be supported.

- 411 When a CIM\_EnabledLogicalElementCapabilities instance is associated with the CIM\_ProcessorCore

- 412 instance and the value of the CIM\_EnabledLogicalElementCapabilities.RequestedStatesSupported

- 413 property is not an empty array, processor core state management shall be supported.

### 414 **7.6.3** CIM\_ProcessorCore.RequestedState

- 415 The CIM\_ProcessorCore.RequestedState property shall have a value of 12 (Not Applicable) or 5 (No

- 416 Change), or a value contained in the

#### DSP1022

- 417 CIM\_EnabledLogicalElementCapabilities.RequestedStatesSupported property array of the associated

- 418 CIM\_EnabledLogicalElementCapabilities instance (see 7.6.1.1).

- 419 When processor core state management is supported and the RequestStateChange() method is

420 successfully executed, the RequestedState property shall be set to the value of the RequestedState

421 parameter of the RequestStateChange() method. After the RequestStateChange() method has

422 successfully executed, the RequestedState and EnabledState properties shall have equal values with the

423 exception of the transitional requested state 11 (Reset). The value of the RequestedState property may

- 424 also change as a result of a request for a change to the processor's enabled state by a non-CIM

- 425 implementation.

## 426 7.6.3.1 RequestedState — 12 (Not Applicable) value

- 427 When processor core state management is not supported, the value of the

- 428 CIM\_ProcessorCore.RequestedState property shall be 12 (Not Applicable).

### 429 **7.6.3.2** RequestedState — 5 (No Change) value

- 430 When processor core state management is supported, the initial value of the

- 431 CIM\_ProcessorCore.RequestedState property shall be 5 (No Change).

## 432 **7.6.4** Modeling the current enabled state of the processor core

433 The current enabled state of the processor core is described by the

434 CIM\_ProcessorCore.CoreEnabledState and CIM\_ProcessorCore.EnabledState properties. Clauses

435 7.6.4.1 and 7.6.4.2 detail the requirements for implementing these two properties.

436 **7.6.4.1** CIM\_ProcessorCore.CoreEnabledState

437 Table 5 describes the mapping between the values of the CIM\_ProcessorCore.CoreEnabledState

438 property and the corresponding description of the state of the processor core. The CoreEnabledState

439 property shall match the values that are specified in Table 5. When the RequestStateChange() method

440 executes but does not complete successfully, and the processor core is in an indeterminate state, the

441 CoreEnabledState property shall have a value of 0 (Unknown). The value of this property may also 442 change as a result of a change to the processor's enabled state by a non-CIM implementation.

443

### Table 5 – CIM\_ProcessorCore.CoreEnabledState Value Descriptions

| Value | Description                 | Extended Description                                                                                                                                                                        |

|-------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | Unknown                     | Processor core state is indeterminate, or the processor core state management is not supported.                                                                                             |

| 2     | Enabled                     | Processor core shall be enabled.                                                                                                                                                            |

| 3     | Disabled                    | Processor core shall be disabled.                                                                                                                                                           |

| 4     | Core Disabled User          | Processor core shall be disabled through client configuration,<br>which may occur through client invocation of<br>RequestStateChange() or through a non-CIM implementation<br>such as BIOS. |

| 5     | Core Disabled By Post Error | Processor core shall be disabled due to a POST error.                                                                                                                                       |

### 444 **7.6.4.2** CIM\_ProcessorCore.EnabledState

The CIM\_ProcessorCore.EnabledState property shall be implemented in addition to the

446 CIM\_ProcessorCore.CoreEnabledState property. When the CoreEnabledState property value matches a

value in the "CoreEnabledState Value" column in Table 6, the EnabledState property shall have the value

that matches the value in the "EnabledState Value" column in the same row in the table.

| CoreEnabledState Value | Description                 | EnabledState Value | Description                  |

|------------------------|-----------------------------|--------------------|------------------------------|

| 0                      | Unknown                     | 0 or 5             | Unknown or Not<br>Applicable |

| 2                      | Enabled                     | 2                  | Enabled                      |

| 3                      | Disabled                    | 3                  | Disabled                     |

| 4                      | Core Disabled User          | 3                  | Disabled                     |

| 5                      | Core Disabled By Post Error | 3                  | Disabled                     |

### Table 6 – Mapping for the CoreEnabledState property and EnabledState property values

## 450 **7.7 Modeling individual hardware threads**

451 Modeling the individual hardware threads is optional functionality. When hardware threads are modeled,

the implementation shall model processor cores as described in 7.6 and shall instantiate an instance of

453 CIM\_HardwareThread to represent each hardware thread. All the requirements in this clause and its 454 subclauses are applicable when an implementation instantiates the CIM HardwareThread class.

subclauses are applicable when an implementation instantiates the Chin\_Hardware miead

455 The instance of CIM\_HardwareThread shall be associated through an instance of

456 CIM\_ConcreteComponent to only one instance of CIM\_ProcessorCore that represents the processor core 457 that enables the hardware thread (Threading Processor Core).

458 For a given Host Processor, the number of instances of CIM\_HardwareThread that are associated with

Threading Processor Cores, which in turn are associated with the Host Processor, shall be equal to the value of the NumberOfHardwareThreads property of the instance of CIM ProcessorCapabilities that is

461 associated with the Host Processor.

## 462 **7.7.1 Hardware thread capabilities**

463 When the CIM\_EnabledLogicalElementCapabilities class is instantiated to represent the hardware thread

464 capabilities, the instance of CIM\_EnabledLogicalElementCapabilities shall be associated with the

465 CIM\_HardwareThread instance through an instance of CIM\_ElementCapabilities and used for advertising 466 the capabilities of the CIM\_HardwareThread instance.

467 At most one instance of CIM\_EnabledLogicalElementCapabilities shall be associated with a given 468 instance of CIM\_HardwareThread.

## 469 7.7.1.1 CIM\_EnabledLogicalElementCapabilities.RequestedStatesSupported

470 The RequestedStatesSupported property is an array that contains the supported requested states for the

- instance of CIM\_HardwareThread. This property shall be the super set of the values to be used as the

- 472 RequestedState parameter in the RequestStateChange() method (see 8.3). The value of the

473 RequestedStatesSupported property shall be an empty array or contain any combination of the following

474 values: 2 (Enabled), 3 (Disabled), or 11 (Reset).

## 475 7.7.1.2 CIM\_EnabledLogicalElementCapabilities.ElementNameEditSupported

The ElementNameEditSupported property shall have a value of TRUE when the implementation supports client modification of the CIM\_HardwareThread.ElementName property.

## 478 **7.7.1.3** CIM\_EnabledLogicalElementCapabilities.MaxElementNameLen

The MaxElementNameLen property shall be implemented when the ElementNameEditSupported property has a value of TRUE.

#### 481 **7.7.2 Hardware thread state management**

- 482 Hardware thread state management requires that the CIM\_HardwareThread.RequestStateChange()

- 483 method be supported (see 8.3) and the value of the CIM\_HardwareThread.RequestedState property not 484 match 12 (Not Applicable).

#### 485 **7.7.2.1** Hardware thread state management support

- 486 When no CIM\_EnabledLogicalElementCapabilities instance is associated with the CIM\_HardwareThread 487 instance, hardware thread state management shall not be supported.

- When a CIM\_EnabledLogicalElementCapabilities instance is associated with the CIM\_HardwareThread instance but the value of the CIM\_EnabledLogicalElementCapabilities.RequestedStatesSupported property is an empty array, hardware thread state management shall not be supported.

- 491 When a CIM\_EnabledLogicalElementCapabilities instance is associated with the CIM\_HardwareThread

- 492 instance and the value of the CIM\_EnabledLogicalElementCapabilities.RequestedStatesSupported

- 493 property is not an empty array, hardware thread state management shall be supported.

### 494 **7.7.3 CIM\_HardwareThread.RequestedState**

- 495 The CIM\_HardwareThread.RequestedState property shall have a value of 12 (Not Applicable) or 5 (No

- 496 Change), or a value contained in the

- 497 CIM\_EnabledLogicalElementCapabilities.RequestedStatesSupported property array of the associated

- 498 CIM\_EnabledLogicalElementCapabilities instance (see 7.7.1.1).

- 499 When hardware thread state management is supported and the RequestStateChange() method is

- 500 successfully executed, the RequestedState property shall be set to the value of the RequestedState

- 501 parameter of the RequestStateChange() method. After the RequestStateChange() method has

- 502 successfully executed, the RequestedState and EnabledState properties shall have equal values with the

- 503 exception of the transitional requested state 11 (Reset). The value of the RequestedState property may

- also change as a result of a request for a change to the hardware thread's enabled state by a non-CIM implementation.

#### 506 7.7.3.1 RequestedState — 12 (Not Applicable) value

- 507 When hardware thread state management is not supported, the value of the

- 508 CIM\_HardwareThread.RequestedState property shall be 12 (Not Applicable).

### 509 **7.7.3.2** RequestedState — 5 (No Change) value

- 510 When hardware thread state management is supported, the initial value of the

- 511 CIM\_HardwareThread.RequestedState property shall be 5 (No Change).

## 512 **7.7.4 CIM\_HardwareThread.EnabledState**

- 513 Table 7 describes the mapping between the values of the CIM\_HardwareThread.EnabledState property

- and the corresponding description of the state of the hardware thread. The EnabledState property shall

- 515 match the values that are specified in Table 7. When the RequestStateChange() method executes but

- does not complete successfully, and the hardware thread is in an indeterminate state, the EnabledState

- 517 property shall have a value of 5 (Not Applicable). The value of this property may also change as a result 518 of a change to the hardware thread's enabled state by a non-CIM implementation.

Table 7 – CIM\_HardwareThread.EnabledState Value Descriptions

| Value | Description    | Extended Description                                                                          |  |

|-------|----------------|-----------------------------------------------------------------------------------------------|--|

| 2     | Enabled        | Hardware thread shall be enabled.                                                             |  |

| 3     | Disabled       | Hardware thread shall be disabled.                                                            |  |

| 5     | Not Applicable | Hardware thread state is indeterminate, or hardware thread state management is not supported. |  |

## 520 **7.8 Modeling cache memory**

521 Modeling the cache memory of the processor is optional. The implementation may instantiate instances of 522 CIM\_Memory to represent the cache memory. All the requirements in this clause and its subclauses are 523 applicable when an implementation instantiates the CIM\_Memory class that represents cache memory.

524 A single instance of CIM\_Memory shall exist for each discrete cache memory. When the cache memory is 525 shared, the single instance of CIM\_Memory shall be associated with multiple instances of CIM\_Processor

526 or CIM\_ProcessorCore. When the cache memory is not shared, the instance of CIM\_Memory shall be

- 527 associated with exactly one instance of CIM\_Processor or CIM\_ProcessorCore.

- 528 When the optional behavior described in 7.6 is implemented, each instance of CIM\_Memory that

- 529 represents the cache memory used by the processor core shall be associated with the instance of

- 530 CIM\_ProcessorCore that represents the processor core through an instance of

- 531 CIM\_AssociatedCacheMemory and shall not be associated with the Host Processor of the core.

532 When the optional behavior described in 7.6 is not implemented, each instance of CIM\_Memory that

- 533 represents the cache memory used by the processor shall be associated through an instance of the

- 534 CIM\_AssociatedCacheMemory to the instance of CIM\_Processor.

## 535 **7.8.1 Cache memory capabilities**

536 When the CIM\_EnabledLogicalElementCapabilities class is instantiated to represent the cache memory

- 537 capabilities, the instance of CIM\_EnabledLogicalElementCapabilities shall be associated with the

- 538 CIM\_Memory instance through an instance of CIM\_ElementCapabilities and used for advertising the 539 capabilities of the CIM\_Memory instance.

- 540 At most one instance of CIM\_EnabledLogicalElementCapabilities shall be associated with a given 541 instance of CIM\_Memory.

## 542 7.8.1.1 CIM\_EnabledLogicalElementCapabilities.RequestedStatesSupported

- 543 The RequestedStatesSupported property is an array that contains the supported requested states for the 544 instance of CIM Memory. This property shall be the super set of the values to be used as the

- 544 instance of CIM\_Memory. This property shall be the super set of the values to be used as the 545 RequestedState parameter in the RequestStateChange() method (see 8.4). The value of the

- 546 RequestedStatesSupported property shall be an empty array or contain any combination of the following

- 547 values: 2 (Enabled), 3 (Disabled), or 11 (Reset).

## 548 **7.8.1.2 CIM\_EnabledLogicalElementCapabilities.ElementNameEditSupported**

549 The ElementNameEditSupported property shall have a value of TRUE when the implementation supports 550 client modification of the CIM\_Memory.ElementName property.

## 551 **7.8.1.3 CIM\_EnabledLogicalElementCapabilities.MaxElementNameLen**

552 The MaxElementNameLen property shall be implemented when the ElementNameEditSupported 553 property has a value of TRUE.

### 554 **7.8.2 Cache memory state management**

555 Cache memory state management requires that the CIM\_Memory.RequestStateChange() method be

supported (see 8.4) and the value of the CIM\_Memory.RequestedState property not match 12 (Not

Applicable).

## 558 **7.8.2.1 Cache memory state management support**

- 559 When no CIM\_EnabledLogicalElementCapabilities instance is associated with the CIM\_Memory instance, 560 cache memory state management shall not be supported.

- 561 When a CIM\_EnabledLogicalElementCapabilities instance is associated with the CIM\_Memory instance 562 but the value of the CIM\_EnabledLogicalElementCapabilities.RequestedStatesSupported property is an 563 empty array, cache memory state management shall not be supported.

- 564 When a CIM\_EnabledLogicalElementCapabilities instance is associated with the CIM\_Memory instance 565 and the value of the CIM\_EnabledLogicalElementCapabilities.RequestedStatesSupported property is not 566 an empty array, cache memory state management shall be supported.

## 567 **7.8.3 CIM\_Memory.RequestedState**

- 568 The CIM\_Memory.RequestedState property shall have a value of 12 (Not Applicable) or 5 (No Change), 569 or a value contained in the CIM\_EnabledLogicalElementCapabilities.RequestedStatesSupported property 570 array of the associated CIM\_EnabledLogicalElementCapabilities instance (see 7.8.1.1).

- 571 When cache memory state management is supported and the RequestStateChange() method is 572 successfully executed, the RequestedState property shall be set to the value of the RequestedState 573 parameter of the RequestStateChange() method. After the RequestStateChange() method has 574 successfully executed, the RequestedState and EnabledState properties shall have equal values with the 575 exception of the transitional requested state 11 (Reset). The value of the RequestedState property may

- also change as a result of a request for a change to the cache memory's enabled state by a non-CIM

- 577 implementation.

### 578 **7.8.3.1** RequestedState — 12 (Not Applicable) value

579 When cache memory state management is not supported, the value of the CIM\_Memory.RequestedState 580 property shall be 12 (Not Applicable).

### 581 **7.8.3.2 RequestedState — 5 (No Change) value**

- 582 When cache memory state management is supported, the initial value of the

- 583 CIM\_Memory.RequestedState property shall be 5 (No Change).

## 584 **7.8.4 CIM\_Memory.EnabledState**

585 Table 8 describes the mapping between the values of the CIM\_Memory.EnabledState property and the 586 corresponding description of the state of the cache memory. The EnabledState property shall match the

- values that are specified in Table 8. When the RequestStateChange() method executes but does not

- 588 complete successfully, and the cache memory is in an indeterminate state, the EnabledState property

- shall have value of 5 (Not Applicable). The value of this property may also change as a result of a change

to the cache memory's enabled state by a non-CIM implementation.

Table 8 – CIM\_Memory.EnabledState value descriptions

| [ | Value | Description    | Extended Description                                                                    |  |

|---|-------|----------------|-----------------------------------------------------------------------------------------|--|

|   | 2     | Enabled        | Cache memory shall be enabled.                                                          |  |

|   | 3     | Disabled       | Cache memory shall be disabled.                                                         |  |

|   | 5     | Not Applicable | Cache memory state is indeterminate, or cache memory state management is not supported. |  |

## **592 7.9 Modeling physical aspects of processor and cache memory**

593 The <u>*Physical Asset Profile*</u> may be implemented to model the physical aspects of a processor, including 594 the asset information of the processor or the internal or off-chip cache memory.

595 When the processor's or internal cache memory's physical aspects are represented, a CIM\_Chip instance

shall be instantiated and associated with the instance of CIM\_Processor or with any instances of

597 CIM\_Memory that represent the internal cache through instances of CIM\_Realizes.

- 598 When the off-chip cache memory is represented along with its physical aspects, a CIM\_PhysicalMemory 599 instance shall be instantiated and associated with the instance of CIM\_Memory through an instance of 600 CIM\_Realizes.

- 601 When processor cores or hardware threads for the processor are modeled with the physical aspects of 602 the processor, the instances of CIM\_ProcessorCore and CIM\_HardwareThread shall not be associated 603 with the instance of CIM\_Chip that represents the physical aspects of the processor.

- The configuration capacity of the managed system for processors may be modeled using the optional behavior specified in the "Modeling Configuration Capacity" clause of the <u>*Physical Asset Profile*</u>.

## 606 8 Methods

This clause details the requirements for supporting intrinsic operations and extrinsic methods for the CIM elements defined by this profile.

## 609 8.1 CIM\_Processor.RequestStateChange()

- 610 Invocation of the CIM\_Processor.RequestStateChange() method changes the element's state to the 611 value that is specified in the RequestedState parameter.

- Return code values for the RequestStateChange() method shall be as specified in Table 9. Parameters

of the RequestStateChange() method are specified in Table 10.

- 614 When processor state management is supported, the RequestStateChange() method shall be 615 implemented and shall not return a value of 1 (Not Supported) (see 7.3.1).

- 616 Invoking the CIM\_Processor.RequestStateChange() method multiple times could result in earlier 617 requests being overwritten or lost.

- 618 No standard messages are defined for this method.

Table 9 – CIM\_Processor.RequestStateChange() method: Return code values

| Value | Description                                    |

|-------|------------------------------------------------|

| 0     | Request was successfully executed.             |

| 1     | Method is not supported in the implementation. |

| 2     | Error occurred                                 |

| 4096  | Job started                                    |

620

#### Table 10 – CIM\_Processor.RequestStateChange() method: Parameters

| Qualifiers | Name           | Туре                | Description/Values                                                                         |

|------------|----------------|---------------------|--------------------------------------------------------------------------------------------|

| IN, REQ    | RequestedState | uint16              | Valid state values:                                                                        |

|            |                |                     | 2 (Enabled)                                                                                |

|            |                |                     | 3 (Disabled)                                                                               |

|            |                |                     | 11 (Reset)                                                                                 |

| OUT        | Job            | CIM_ConcreteJob REF | Returned if job started                                                                    |

| IN, REQ    | TimeoutPeriod  | datetime            | Client-specified maximum amount of time the transition to a new state is supposed to take: |

|            |                |                     | 0 or NULL – No time requirements                                                           |

|            |                |                     | <interval> – Maximum time allowed</interval>                                               |

## 621 8.2 CIM\_ProcessorCore.RequestStateChange()

622 Invocation of the CIM\_ProcessorCore.RequestStateChange() method changes the element's state to the 623 value that is specified in the RequestedState parameter.

- 624 Return code values for the RequestStateChange() method shall be as specified in Table 11. Parameters 625 of the RequestStateChange() method are specified in Table 12.

- When processor core state management is supported, the RequestStateChange() method shall be implemented and shall not return a value of 1 (Not Supported) (see 7.6.2.1).

- 628 Invoking the CIM\_ProcessorCore.RequestStateChange() method multiple times could result in earlier 629 requests being overwritten or lost.

- 630 No standard messages are defined for this method.

631

### Table 11 – CIM\_ProcessorCore.RequestStateChange() method: Return code values

| Value | Description                                    |

|-------|------------------------------------------------|

| 0     | Request was successfully executed.             |

| 1     | Method is not supported in the implementation. |

| 2     | Error occurred                                 |

| 4096  | Job started                                    |

| Qualifiers | Name           | Туре                | Description/Values                                                                         |

|------------|----------------|---------------------|--------------------------------------------------------------------------------------------|

| IN, REQ    | RequestedState | uint16              | Valid state values:                                                                        |

|            |                |                     | 2 (Enabled)                                                                                |

|            |                |                     | 3 (Disabled)                                                                               |

|            |                |                     | 11 (Reset)                                                                                 |

| OUT        | Job            | CIM_ConcreteJob REF | Returned if job started                                                                    |

| IN, REQ    | TimeoutPeriod  | datetime            | Client-specified maximum amount of time the transition to a new state is supposed to take: |

|            |                |                     | 0 or NULL – No time requirements                                                           |

|            |                |                     | <interval> – Maximum time allowed</interval>                                               |

## Table 12 – CIM\_ProcessorCore.RequestStateChange() method: Parameters

## 633 8.3 CIM\_HardwareThread.RequestStateChange()

634 Invocation of the CIM\_HardwareThread.RequestStateChange() method changes the element's state to 635 the value that is specified in the RequestedState parameter.

Return code values for the RequestStateChange() method shall be as specified in Table 13. Parameters

of the RequestStateChange() method are specified in Table 14.

638 When hardware thread state management is supported, the RequestStateChange() method shall be 639 implemented and shall not return a value of 1 (Not Supported) (see 7.7.2.1).

640 Invoking the CIM\_HardwareThread.RequestStateChange() method multiple times could result in earlier 641 requests being overwritten or lost.

642 No standard messages are defined for this method.

643

### Table 13 – CIM\_HardwareThread.RequestStateChange() method: Return code values

| Value | Description                                    |

|-------|------------------------------------------------|

| 0     | Request was successfully executed.             |

| 1     | Method is not supported in the implementation. |

| 2     | Error occurred                                 |

| 4096  | Job started                                    |

644

### Table 14 – CIM\_HardwareThread.RequestStateChange() method: Parameters

| Qualifiers | Name           | Туре                | Description/Values                                                                         |

|------------|----------------|---------------------|--------------------------------------------------------------------------------------------|

| IN, REQ    | RequestedState | uint16              | Valid state values:                                                                        |

|            |                |                     | 2 (Enabled)                                                                                |

|            |                |                     | 3 (Disabled)                                                                               |

|            |                |                     | 11 (Reset)                                                                                 |

| OUT        | Job            | CIM_ConcreteJob REF | Returned if job started                                                                    |

| IN, REQ    | TimeoutPeriod  | datetime            | Client-specified maximum amount of time the transition to a new state is supposed to take: |

|            |                |                     | 0 or NULL – No time requirements                                                           |

|            |                |                     | <interval> – Maximum time allowed</interval>                                               |

#### DSP1022

## 645 8.4 CIM\_Memory.RequestStateChange()

- 646 Invocation of the CIM\_Memory.RequestStateChange() method changes the element's state to the value 647 that is specified in the RequestedState parameter.

- 648 Return code values for the RequestStateChange() method shall be as specified in Table 15. Parameters 649 of the RequestStateChange() method are specified in Table 16.

- 650 When memory state management is supported, the RequestStateChange() method shall be implemented 651 and shall not return a value of 1 (Not Supported) (see 7.8.2.1).

- Invoking the CIM\_Memory.RequestStateChange() method multiple times could result in earlier requests

being overwritten or lost.

- No standard messages are defined for this method.

#### 655

#### Table 15 – CIM\_Memory.RequestStateChange() method: Return code values

| Value | Description                                    |

|-------|------------------------------------------------|

| 0     | Request was successfully executed.             |

| 1     | Method is not supported in the implementation. |

| 2     | Error occurred                                 |

| 4096  | Job started                                    |

656

#### Table 16 – CIM\_Memory.RequestStateChange() method: Parameters

| Qualifiers | Name           | Туре                | Description/Values                                                                         |

|------------|----------------|---------------------|--------------------------------------------------------------------------------------------|

| IN, REQ    | RequestedState | uint16              | Valid state values:                                                                        |

|            |                |                     | 2 (Enabled)                                                                                |

|            |                |                     | 3 (Disabled)                                                                               |

|            |                |                     | 11 (Reset)                                                                                 |

| OUT        | Job            | CIM_ConcreteJob REF | Returned if job started                                                                    |